#### VItralow Jitter Multioutput Clock Synthesizer with Integrated VCO

#### **FEATURES**

- Low Noise Integer-N PLL with Integrated VCO

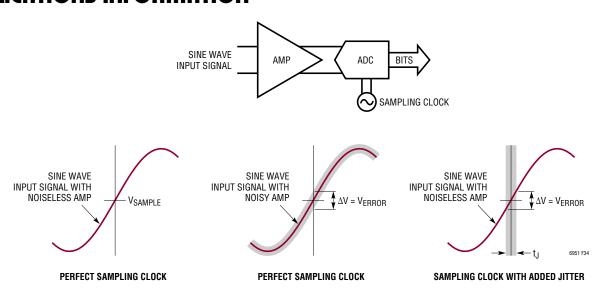

- Output Jitter:

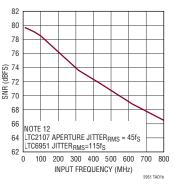

- 90fs RMS (12kHz to 20MHz)

- 115fs RMS (ADC SNR Method)

- Noise Floor = -165dBc/Hz at 250MHz

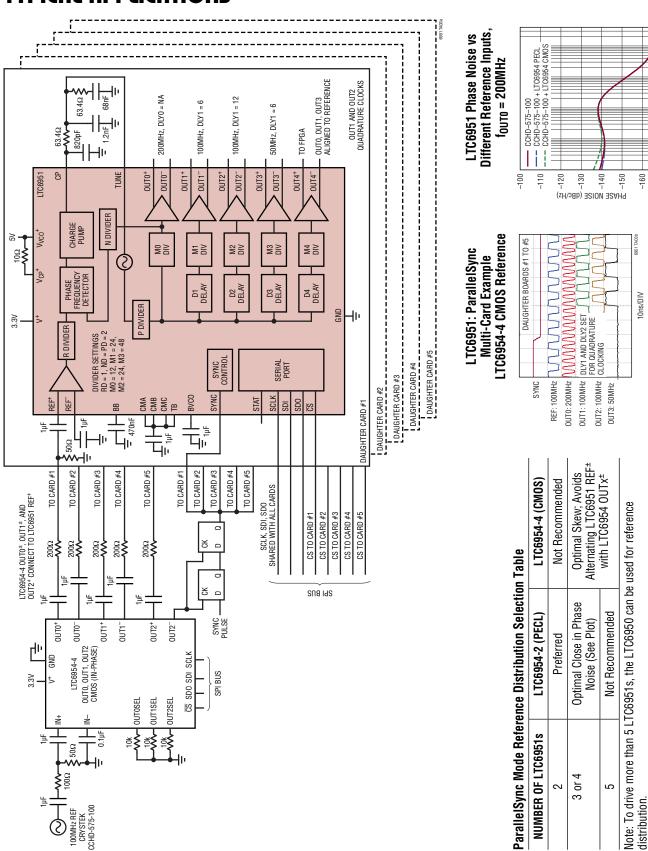

- EZSync<sup>TM</sup>, ParallelSync<sup>TM</sup> Multichip Synchronization

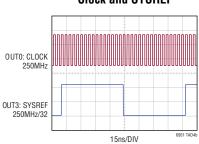

- SYSREF Generation for JESD204B. Subclass 1

- Output Frequency Range:

- 1.95MHz to 2.5GHz (LTC6951)

- 2.1MHz to 2.7GHz (LTC6951-1)

- –229dBc/Hz Normalized In-Band Phase Noise Floor

- -277dBc/Hz Normalized In-Band 1/f Noise

- Five Independent, Low Noise Outputs

- Reference Input Frequency up to 425MHz

- LTC6951Wizard<sup>™</sup> Software Design Tool Support

- -40°C to 105°C Operating Junction Temperature Range

#### **APPLICATIONS**

- High Performance Data Converter Clocking

- Wireless Infrastructure

- Test and Measurement

#### DESCRIPTION

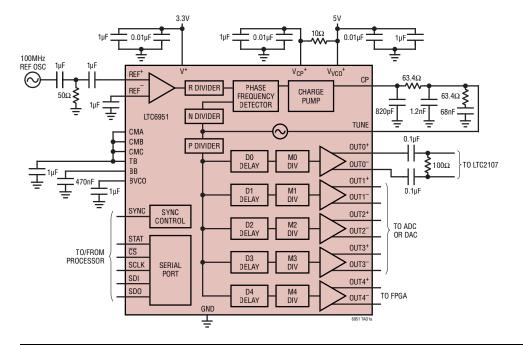

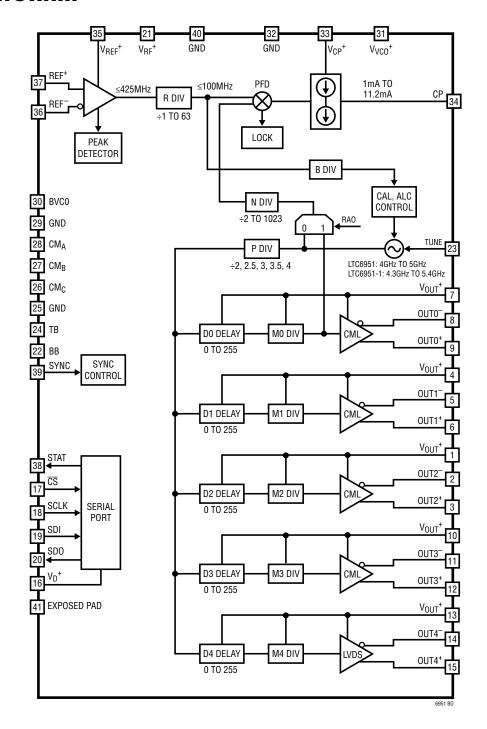

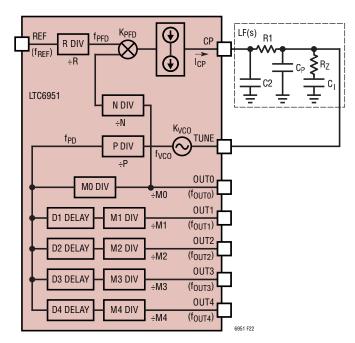

The LTC®6951 is a high performance, low noise, Phase Locked Loop (PLL) with a fully integrated VCO. The low noise VCO uses no external components and is internally calibrated to the correct output frequency with no external system support.

The clock generation section provides five outputs based on the VCO prescaler signal with individual dividers for each output. Four outputs feature very low noise, low skew CML logic. The fifth output is low noise LVDS. All outputs can be synchronized and set to precise phase alignment using the programmable delays.

Choose the LTC6951-1 if any desired output frequency falls in the ranges 2.5GHz to 2.7GHz, 1.66GHz to 1.8GHz, or 1.25GHz to 1.35GHz. Choose the LTC6951 for all other frequencies.

LT, LTC, LTM, Linear Technology and the Linear logo are registered trademarks and EZSync, LTC6951Wizard and ParallelSync are trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners. Protected by U.S. Patents, including 8319551 and 8819472.

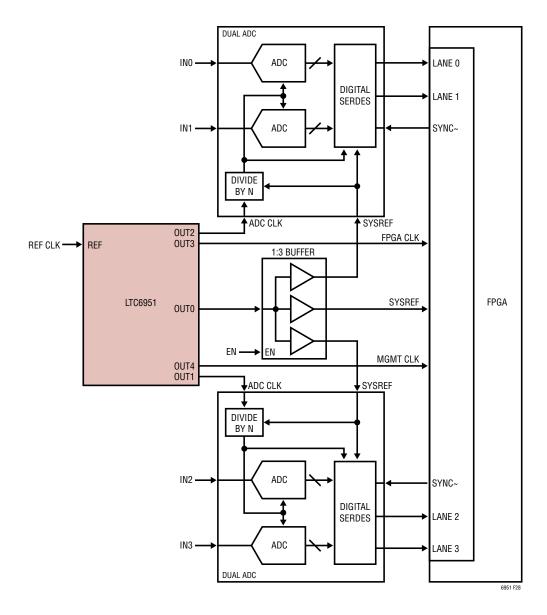

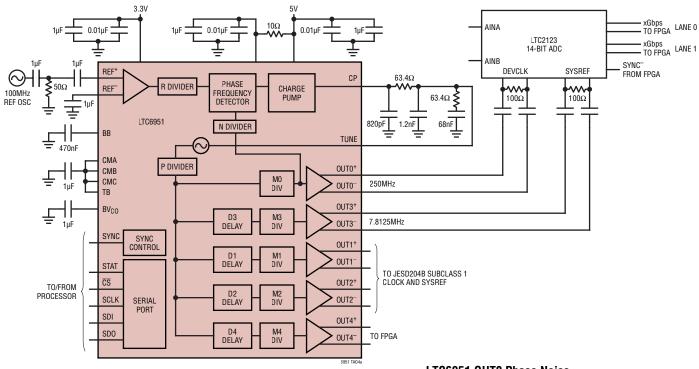

#### TYPICAL APPLICATION

## SNR vs Input Frequency of LTC6951 Clocking an LTC2107, f<sub>S</sub> = 210Msps, A<sub>IN</sub> = -3dBFS

6951fa

#### **ABSOLUTE MAXIMUM RATINGS**

#### (Note 1)

####

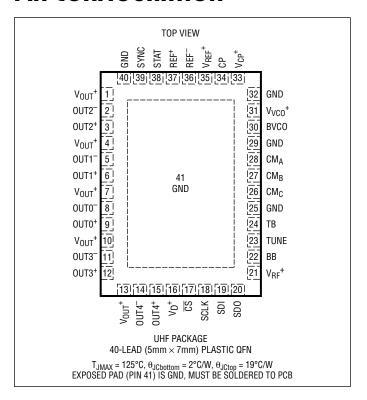

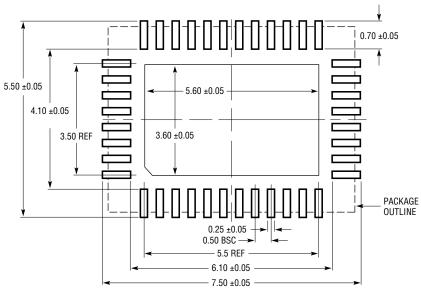

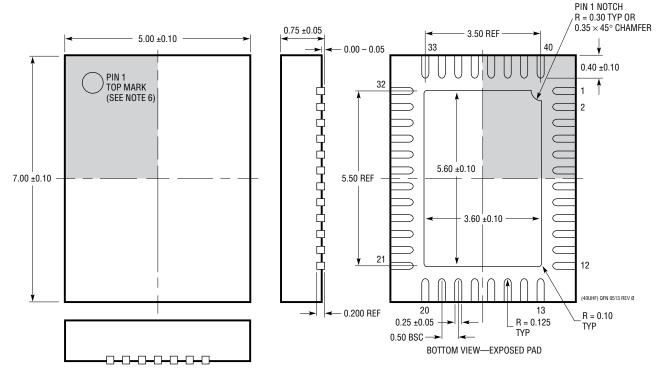

#### PIN CONFIGURATION

#### ORDER INFORMATION

(http://www.linear.com/product/LTC6951#orderinfo)

| LEAD FREE FINISH  | TAPE AND REEL       | PART MARKING | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|-------------------|---------------------|--------------|---------------------------------|-------------------|

| LTC6951IUHF#PBF   | LTC6951IUHF#TRPBF   | 6951         | 40-Lead (5mm × 7mm) Plastic QFN | -40°C to 105°C    |

| LTC6951IUHF-1#PBF | LTC6951IUHF-1#TRPBF | 69511        | 40-Lead (5mm × 7mm) Plastic QFN | -40°C to 105°C    |

Consult LTC Marketing for parts specified with wider operating temperature ranges.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

| SYMBOL            | PARAMETER                                    | CONDITIONS                                                                       |   | MIN        | TYP        | MAX        | UNITS             |

|-------------------|----------------------------------------------|----------------------------------------------------------------------------------|---|------------|------------|------------|-------------------|

| Referenc          | e Inputs (REF+, REF <sup>-</sup> )           | •                                                                                |   |            |            |            | 1                 |

| f <sub>REF</sub>  | Input Frequency                              |                                                                                  | • | 1          | -          | 425        | MHz               |

| $V_{REF}$         | Input Signal Level                           | Single-Ended                                                                     | • | 0.5        | 2          | 2.7        | V <sub>P-P</sub>  |

|                   | Minimum Input Slew Rate                      |                                                                                  |   |            | 20         |            | V/µs              |

|                   | Input Duty Cycle                             |                                                                                  |   |            | 50         |            | %                 |

|                   | Self-Bias Voltage                            |                                                                                  | • | 1.65       | 1.85       | 2.25       | V                 |

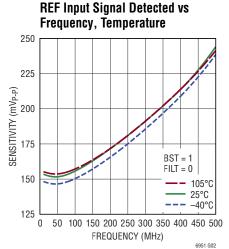

|                   | Input Signal Detected                        | REFOK = 1, PDREFPK = 0<br>10MHz ≤ f <sub>REF</sub> ≤ 425MHz, Sine Wave           | • | 350        |            |            | mV <sub>P-P</sub> |

|                   | Input Signal Not Detected                    | REFOK = 0, PDREFPK = 0<br>10MHz $\leq$ f <sub>REF</sub> $\leq$ 425MHz, Sine Wave | • |            |            | 100        | mV <sub>P-P</sub> |

|                   | Input Resistance                             | Differential                                                                     | • | 2.6        | 4.2        | 6.1        | kΩ                |

|                   | Input Capacitance                            | Differential                                                                     |   |            | 7          |            | pF                |

| VCO               |                                              |                                                                                  |   |            |            |            |                   |

| f <sub>VCO</sub>  | Frequency Range                              | LTC6951 (Note 3)<br>LTC6951-1 (Note 3)                                           | • | 4.0<br>4.3 |            | 5.0<br>5.4 | GHz<br>GHz        |

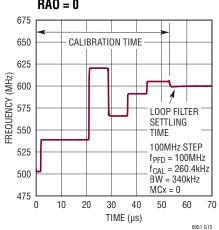

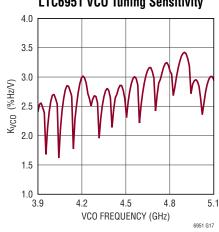

| K <sub>VCO</sub>  | Tuning Sensitivity                           | (Notes 3, 4)                                                                     |   |            | 2.5 to 3.7 |            | %Hz/V             |

| Phase/Fr          | requency Detector (PFD)                      |                                                                                  |   |            |            |            |                   |

| f <sub>PFD</sub>  | Input Frequency                              |                                                                                  | • |            |            | 100        | MHz               |

| Charge P          | Pump (CP)                                    |                                                                                  |   |            |            |            |                   |

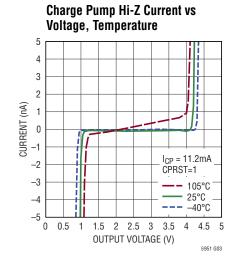

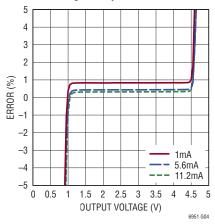

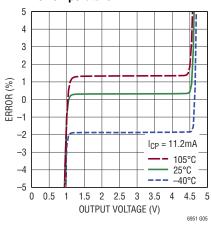

| I <sub>CP</sub>   | Output Current Range                         | 8 Settings (see Table 8)                                                         |   | 1.0        |            | 11.2       | mA                |

|                   | Output Current Source/Sink Accuracy          | All Settings, V(CP) = 2.3V                                                       |   |            |            | ±6         | %                 |

|                   | Output Current Source/Sink Matching          | $I_{CP} = 1.0$ mA to 1.4mA, $V(CP) = 2.3V$                                       |   |            |            | ±3.5       | %                 |

|                   |                                              | $I_{CP} = 2.0$ mA to 11.2mA, $V(CP) = 2.3V$                                      |   |            |            | ±2         | %                 |

|                   | Output Current vs Output Voltage Sensitivity | (Note 5)                                                                         | • |            | 0.1        | 0.5        | %/V               |

|                   | Output Current vs Temperature                | V(CP) = 2.3V                                                                     | • |            | 140        |            | ppm/°C            |

|                   | Output Hi-Z Leakage Current                  | I <sub>CP</sub> = 1mA (Note 5)                                                   |   |            | 0.5        |            | nA                |

|                   |                                              | I <sub>CP</sub> = 11.2mA (Note 5)                                                |   |            | 5          |            | nA                |

| $V_{MID}$         | Mid-Supply Output Bias Ratio                 | Referred to (V <sub>CP</sub> <sup>+</sup> – GND)                                 |   |            | 0.48       |            | V/V               |

| Referenc          | e Divider (R)                                |                                                                                  |   |            |            |            |                   |

| R                 | Divide Range                                 | All Integers Included                                                            | • | 1          |            | 63         | Counts            |

| VCO Divi          | der (N)                                      |                                                                                  |   |            |            |            |                   |

| N                 | Divide Range                                 | All Integers Included, RAO = 0                                                   | • | 32         |            | 1023       | Counts            |

|                   |                                              | All Integers Included, RAO = 1                                                   | • | 2          |            | 511        | Counts            |

| VCO Pres          | scaler Divider (P)                           |                                                                                  |   |            |            |            |                   |

| P                 | Divide Range                                 | 2, 2.5, 3, 3.5, 4 (see Table 14)                                                 | • | 2          |            | 4          | Counts            |

| Digital P         | in Specifications                            |                                                                                  |   |            |            |            |                   |

| V <sub>IH</sub>   | High Level Input Voltage                     | CS, SDI, SCLK, SYNC                                                              | • | 1.55       |            |            | V                 |

| V <sub>IL</sub>   | Low Level Input Voltage                      | CS, SDI, SCLK, SYNC                                                              | • |            |            | 8.0        | V                 |

| V <sub>IHYS</sub> | Input Voltage Hysteresis                     | CS, SDI, SCLK, SYNC                                                              |   |            | 250        |            | m۷                |

|                   | Input Current                                | CS, SDI, SCLK, SYNC                                                              | • |            |            | ±1         | μА                |

| I <sub>OH</sub>   | High Level Output Current                    | SDO and STAT, $V_{OH} = V_D^+ - 400 \text{mV}$                                   | • |            | -3.3       | -1.9       | mA                |

| I <sub>OL</sub>   | Low Level Output Current                     | SDO and STAT, V <sub>OL</sub> = 400mV                                            | • | 2.0        | 3.4        |            | mA                |

| ${\bf SYMBOL}$       | PARAMETER                                              | CONDITIONS                                                                                          |           | MIN         | TYP                      | MAX        | UNITS            |

|----------------------|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------|-------------|--------------------------|------------|------------------|

|                      | SDO Hi-Z Current                                       |                                                                                                     | •         |             |                          | ±1         | μА               |

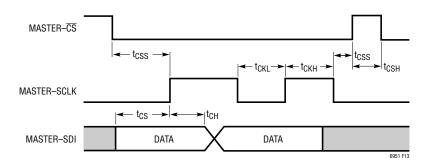

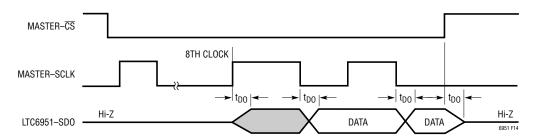

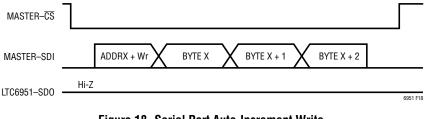

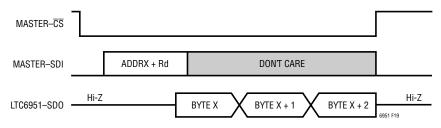

| Digital Ti           | ming Specifications (See Figure 13 and F               | igure 14)                                                                                           |           |             |                          |            |                  |

| t <sub>CKH</sub>     | SCLK High Time                                         |                                                                                                     | •         | 25          |                          |            | ns               |

| t <sub>CKL</sub>     | SCLK Low Time                                          |                                                                                                     | •         | 25          |                          |            | ns               |

| t <sub>CSS</sub>     | CS Setup Time                                          |                                                                                                     | •         | 10          |                          |            | ns               |

| t <sub>CSH</sub>     | CS High Time                                           |                                                                                                     | •         | 10          |                          |            | ns               |

| t <sub>CS</sub>      | SDI to SCLK Setup Time                                 |                                                                                                     | •         | 6           |                          |            | ns               |

| t <sub>CH</sub>      | SDI to SCLK Hold Time                                  |                                                                                                     | •         | 6           |                          |            | ns               |

| $\overline{t_{DO}}$  | SCLK to SDO Time                                       | to V <sub>IH</sub> /V <sub>IL</sub> /Hi-Z with 30pF Load                                            | •         |             |                          | 16         | ns               |

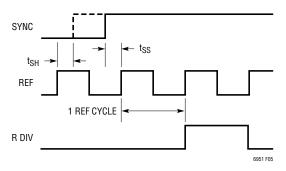

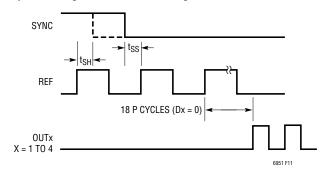

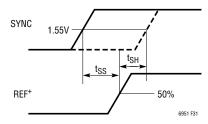

| SYNC Tin             | ning Specifications (See Figure 31 and Fig             | gure 32)                                                                                            |           |             |                          |            |                  |

| t <sub>SYNCH</sub>   | SYNC High Time                                         |                                                                                                     | •         | 1           |                          |            | ms               |

| t <sub>SYNCL</sub>   | SYNC Low Time                                          |                                                                                                     | •         | 1           |                          |            | ms               |

|                      | SYNC Skew                                              | EZSync, Part to Part                                                                                |           |             |                          | 10         | μs               |

| t <sub>SS</sub>      | SYNC to REF Setup Time                                 | (See Note 6)                                                                                        | •         | 1           |                          | ,          | ns               |

| t <sub>SH</sub>      | SYNC to REF Hold Time                                  | (See Note 6)                                                                                        | •         | 1           |                          |            | ns               |

| Output Di            | ividers (M0, M1, M2, M3 and M4)                        |                                                                                                     |           |             |                          |            |                  |

| Mx                   | Output Divider Range (x = 0 to 4)                      | 16 Settings (See Table 15)                                                                          | •         | 1           |                          | 512        | Counts           |

| Dx                   | Output Divider Delay (x = 0 to 4)                      | P Cycles, All Integers Included                                                                     | •         | 0           |                          | 255        | Cycles           |

| CML Cloc             | ck Outputs (OUTO+, OUTO-, OUT1+, OUT1-,                | , OUT2+, OUT2-, OUT3+, OUT3-), Differential Term                                                    | ination = | : 100Ω U    | nless Otherv             | ise Noted  |                  |

| f <sub>OUT</sub>     | LTC6951 Output Frequency                               |                                                                                                     | •         | 1.95        |                          | 2500       | MHz              |

|                      |                                                        | f <sub>OUT</sub> /2 Subharmonic Generated,<br>P = 2.5, Mx = 1 (Note 16)                             | •         | 1667        |                          | 2000       | MHz              |

|                      |                                                        | f <sub>OUT</sub> /2 Subharmonic Generated,<br>P = 3.5, Mx = 1 (Note 16)                             | •         | 1250        |                          | 1333       | MHz              |

|                      | LTC6951-1 Output Frequency                             |                                                                                                     | •         | 2.1         |                          | 2700       | MHz              |

|                      |                                                        | f <sub>OUT</sub> /2 Subharmonic Generated,<br>P = 2.5, Mx = 1 (Note 16)                             | •         | 1800        |                          | 2150       | MHz              |

|                      |                                                        | f <sub>OUT</sub> /2 Subharmonic Generated,<br>P = 3.5, Mx = 1 (Note 16)                             | •         | 1350        |                          | 1433       | MHz              |

|                      | Output High Voltage                                    |                                                                                                     |           |             | $V_{OUT}^+ - 0.9$        |            | V                |

|                      | Output Low Voltage                                     |                                                                                                     |           |             | V <sub>OUT</sub> + – 1.3 |            | V                |

|                      | Output Differential Voltage                            |                                                                                                     | •         | 350         | 440                      | 520        | mV <sub>PK</sub> |

|                      | Output Resistance                                      | Differential, No Termination                                                                        |           |             | 100                      |            | Ω                |

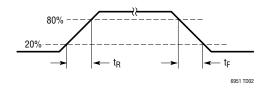

| $t_R$                | Output Rise Time, 20% to 80%                           |                                                                                                     |           |             | 50                       |            | ps               |

| t <sub>F</sub>       | Output Fall Time, 80% to 20%                           |                                                                                                     |           |             | 50                       |            | ps               |

|                      | Output Duty Cycle                                      | $P = 2, 3, 4 \text{ all Mx}, P = 2.5, 3.5 \text{ Mx} \ge 2$<br>P = 2.5,  Mx = 1<br>P = 3.5,  Mx = 1 | •         | 45          | 50<br>40<br>57           | 55         | %<br>%<br>%      |

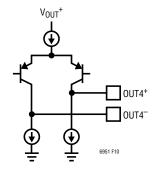

| LVDS CIn             | Lock Outputs (OUT4+, OUT4-), Differential T            | ,                                                                                                   |           |             | <u> </u>                 |            |                  |

| f <sub>OUTLVDS</sub> | LTC6951 Output Frequency<br>LTC6951-1 Output Frequency |                                                                                                     | •         | 1.95<br>2.1 |                          | 800<br>800 | MHz<br>MHz       |

|                      | Differential Output Voltage                            |                                                                                                     | -         | 300         | 380                      | 450        | mV <sub>PK</sub> |

| SYMBOL               | PARAMETER                                                                        | CONDITIONS                                                                    |   | MIN  | TYP  | MAX  | UNITS  |

|----------------------|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------|---|------|------|------|--------|

| $ \Delta V_{OD} $    | Delta V <sub>OD</sub>                                                            |                                                                               | • |      | 5    | 50   | mV     |

| V <sub>OS</sub>      | Output Offset Voltage                                                            |                                                                               |   |      | 1.23 |      | V      |

| $\Delta V_{0S}$      | Delta V <sub>OS</sub>                                                            |                                                                               | • |      | 5    | 50   | mV     |

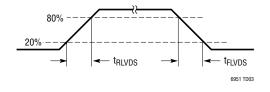

| t <sub>RLVDS</sub>   | Output Rise Time, 20% to 80%                                                     |                                                                               |   |      | 200  |      | ps     |

| t <sub>FLVDS</sub>   | Output Fall Time, 80% to 20%                                                     |                                                                               |   |      | 200  |      | ps     |

|                      | Short Circuit Current to Common                                                  | Shorted to GND                                                                | • |      | 7.4  | 24   | mA     |

|                      | Short Circuit to Complementary                                                   |                                                                               |   |      | 3.7  |      | mA     |

|                      | Output Duty Cycle                                                                | M4 ≥ 2                                                                        | • | 45   | 50   | 55   | %      |

| Clock Out            | tput Skews (OUTO+, OUTO <sup>-</sup> , OUT1+, OUT1 <sup>-</sup> , OUT            | 2+, OUT2 <sup>-</sup> , OUT3+, OUT3 <sup>-</sup> , OUT4+, OUT4 <sup>-</sup> ) |   |      |      |      |        |

| t <sub>SKEW1</sub>   | Maximum Skew, from OUT0 to OUT1                                                  |                                                                               |   |      | ±10  | ±35  | ps     |

| t <sub>SKEW2</sub>   | Maximum Skew, from OUT0 to OUT2                                                  |                                                                               |   |      | ±10  | ±35  | ps     |

| t <sub>SKEW3</sub>   | Maximum Skew, from OUT0 to OUT3                                                  |                                                                               |   |      | ±10  | ±35  | ps     |

| t <sub>SKEW4</sub>   | Maximum Skew, from OUT0 to OUT4                                                  |                                                                               |   |      | ±20  |      | ps     |

|                      | Maximum Skew, All CML Outputs                                                    | One Part                                                                      |   |      | ±20  | ±40  | ps     |

|                      | Maximum Skew, All CML Outputs                                                    | Multiple Parts, RAO = SN = SR = 1                                             |   |      | ±50  | ±100 | ps     |

| Power Su             | ipply Voltages                                                                   |                                                                               | • |      |      |      |        |

|                      | V <sub>REF</sub> <sup>+</sup> Supply Range                                       |                                                                               | • | 3.15 | 3.3  | 3.45 | V      |

|                      | V <sub>OUT</sub> <sup>+</sup> Supply Range                                       |                                                                               | • | 3.15 | 3.3  | 3.45 | V      |

|                      | V <sub>D</sub> <sup>+</sup> Supply Range                                         |                                                                               | • | 3.15 | 3.3  | 3.45 | V      |

|                      | V <sub>RF</sub> <sup>+</sup> Supply Range                                        |                                                                               | • | 3.15 | 3.3  | 3.45 | V      |

|                      | V <sub>VCO</sub> <sup>+</sup> Supply Range                                       |                                                                               | • | 4.75 | 5.0  | 5.25 | V      |

|                      | V <sub>CP</sub> <sup>+</sup> Supply Range                                        |                                                                               | • | 4.2  |      | 5.25 | V      |

| Power Su             | ipply Currents                                                                   |                                                                               |   |      |      |      |        |

| I <sub>DDOUT</sub>   | V <sub>D</sub> +, V <sub>OUT</sub> + Supply Current                              | Digital Inputs at Supply Levels, PDOUT=1                                      |   |      | 32   |      | μА     |

|                      |                                                                                  | Digital Inputs at Supply Levels, SYNC = 3.3V                                  | • |      | 210  | 254  | mA     |

| I <sub>CC-5V</sub>   | Sum V <sub>CP</sub> +, V <sub>VCO</sub> + Supply Currents                        | I <sub>CP</sub> = 11.2mA                                                      | • |      | 56   | 70   | mA     |

|                      |                                                                                  | I <sub>CP</sub> = 1.0mA                                                       | • |      | 33   | 43   | mA     |

|                      |                                                                                  | PDALL = 1                                                                     |   |      | 510  |      | μА     |

| I <sub>CC-3.3V</sub> | Sum V <sub>REF</sub> <sup>+</sup> , V <sub>RF</sub> <sup>+</sup> Supply Currents |                                                                               | • |      | 115  | 130  | mA     |

|                      |                                                                                  | PDALL = 1                                                                     |   |      | 140  |      | μА     |

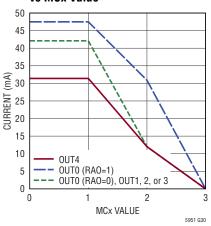

|                      | V <sub>D</sub> +, V <sub>OUT</sub> + Supply Current Deltas                       | MCx[1:0] = 2 (x = 0, 1, 2, or 3)                                              |   |      | -31  |      | mA     |

|                      |                                                                                  | MCx[1:0] = 3 (x = 0, 1, 2, or 3)                                              |   |      | -43  |      | mA     |

|                      |                                                                                  | MC4[1:0] = 2                                                                  |   |      | -21  |      | mA     |

|                      |                                                                                  | MC4[1:0] = 3                                                                  |   |      | -34  |      | mA     |

|                      |                                                                                  | SYNC = V <sub>OUT</sub> <sup>+</sup> or SSYNC = 1                             |   |      | 11   |      | mA     |

| Phase No             | ise and Spurious                                                                 |                                                                               |   |      |      |      |        |

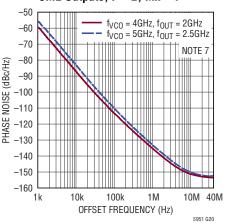

| L <sub>VCO</sub>     | LTC6951 VCO Phase Noise                                                          | 10kHz Offset                                                                  |   |      | -87  |      | dBc/Hz |

|                      | $(f_{VCO} = 4.0GHz, f_{OUTO} = 2.0GHz, P = 2, M0 = 1, Note 7)$                   | 100kHz Offset                                                                 |   |      | -113 |      | dBc/Hz |

|                      | Note 1)                                                                          | 1MHz Offset                                                                   |   |      | -135 |      | dBc/Hz |

| SYMBOL            | PARAMETER                                                                                                                                                            | CONDITIONS                                                                | MIN TYP | MAX | UNITS             |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|---------|-----|-------------------|

|                   | LTC6951 VCO Phase Noise                                                                                                                                              | 10kHz Offset                                                              | -83     |     | dBc/Hz            |

|                   | $(f_{VCO} = 5.0 GHz, f_{OUTO} = 2.5 GHz, P = 2, M0 = 1, Note 7)$                                                                                                     | 100kHz Offset                                                             | -110    |     | dBc/Hz            |

|                   |                                                                                                                                                                      | 1MHz Offset                                                               | -133    |     | dBc/Hz            |

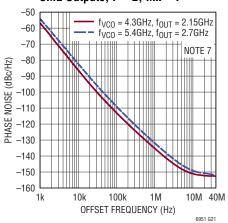

|                   | LTC6951-1 VCO Phase Noise                                                                                                                                            | 10kHz Offset                                                              | -83     |     | dBc/Hz            |

|                   | $(f_{VCO} = 5.4 GHz, f_{OUTO} = 2.7 GHz, P = 2, M0 = 1, Note 7)$                                                                                                     | 100kHz Offset                                                             | -110    |     | dBc/Hz            |

|                   | Note 1)                                                                                                                                                              | 1MHz Offset                                                               | -133    |     | dBc/Hz            |

|                   | LTC6951-1 CML Output Noise/Jitter                                                                                                                                    | Phase Noise 10kHz Offset                                                  | -119    |     | dBc/Hz            |

|                   | $(f_{VCO} = 5.4 GHz, f_{OUTO} = f_{OUT1} = f_{OUT2} = f_{OUT3} = 2.7 GHz, P = 2, M0 = M1 = M2 = M3 = 1,$                                                             | Phase Noise 1MHz Offset                                                   | -129    |     | dBc/Hz            |

|                   | Notes 9, 12)                                                                                                                                                         | Phase Noise 40MHz Offset                                                  | -153    |     | dBc/Hz            |

|                   | Notes 9, 12)                                                                                                                                                         | Jitter, 12kHz to 20MHz Integration BW                                     | 90      |     | fs <sub>RMS</sub> |

|                   |                                                                                                                                                                      | Jitter, 100Hz to f <sub>OUTx</sub> Integration BW                         | 115     |     | fs <sub>RMS</sub> |

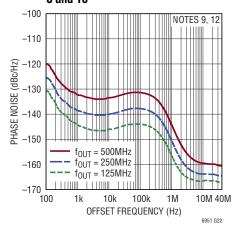

|                   | LTC6951 CML Output Noise/Jitter                                                                                                                                      | Phase Noise 10kHz Offset                                                  | -119    |     | dBc/Hz            |

|                   | $(f_{VCO} = 5.0 \text{GHz}, f_{OUTO} = f_{OUT1} = f_{OUT2} = f_{OUT3} = 2.5 \text{GHz}, P = 2, M0 = M1 = M2 = M3 = 1,$                                               | Phase Noise 1MHz Offset                                                   | -129    |     | dBc/Hz            |

|                   | Notes 9, 12)                                                                                                                                                         | Phase Noise 40MHz Offset                                                  | -153    |     | dBc/Hz            |

|                   |                                                                                                                                                                      | Jitter, 12kHz to 20MHz Integration BW                                     | 90      |     | fs <sub>RMS</sub> |

|                   |                                                                                                                                                                      | Jitter, 100Hz to f <sub>OUTx</sub> Integration BW                         | 115     |     | fs <sub>RMS</sub> |

| -                 | LTC6951 CML Output Noise/Jitter $(f_{VCO} = 5.0 \text{GHz}, f_{OUTO} = f_{OUT1} = f_{OUT2} = f_{OUT3} = 1.25 \text{GHz}, P = 2, M0 = M1 = M2 = M3 = 2, Notes 9, 12)$ | 10kHz Offset                                                              | -125    |     | dBc/Hz            |

|                   |                                                                                                                                                                      | 1MHz Offset                                                               | -135    |     | dBc/Hz            |

|                   |                                                                                                                                                                      | 40MHz Offset                                                              | -156    |     | dBc/Hz            |

|                   |                                                                                                                                                                      | Jitter, 12kHz to 20MHz Integration BW                                     | 88      |     | fs <sub>RMS</sub> |

|                   |                                                                                                                                                                      | Jitter, 100Hz to f <sub>OUTx</sub> Integration BW                         | 115     |     | fs <sub>RMS</sub> |

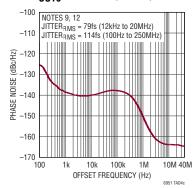

|                   | LTC6951 CML Output Noise/Jitter                                                                                                                                      | 10kHz Offset                                                              | -140    |     | dBc/Hz            |

|                   | $(f_{VCO} = 4.0 \text{GHz}, f_{OUTO} = f_{OUT1} = f_{OUT2} = f_{OUT3} = 250 \text{MHz}, P = 4, M0 = M1 = M2 = M3 = 4,$                                               | 1MHz Offset                                                               | -150    |     | dBc/Hz            |

|                   | Notes 9, 12)                                                                                                                                                         | 40MHz Offset                                                              | -165    |     | dBc/Hz            |

|                   |                                                                                                                                                                      | Jitter, 12kHz to 20MHz Integration BW                                     | 83      |     | fs <sub>RMS</sub> |

|                   |                                                                                                                                                                      | Jitter, 100Hz to f <sub>OUTx</sub> Integration BW                         | 115     |     | fs <sub>RMS</sub> |

|                   | LTC6951 LVDS Output Noise/Jitter                                                                                                                                     | 10kHz Offset                                                              | -140    |     | dBc/Hz            |

|                   | $(f_{VCO} = 4.0GHz, f_{OUT4} = 250MHz, P = 4, M4 = 4, Notes 9, 12)$                                                                                                  | 1MHz Offset                                                               | -150    |     | dBc/Hz            |

|                   | Notes 9, 12)                                                                                                                                                         | 40MHz Offset                                                              | -162    |     | dBc/Hz            |

|                   |                                                                                                                                                                      | Jitter, 12kHz to 20MHz Integration BW                                     | 88      |     | fs <sub>RMS</sub> |

|                   |                                                                                                                                                                      | Jitter, 100Hz to f <sub>OUTx</sub> Integration BW                         | 140     |     | fs <sub>RMS</sub> |

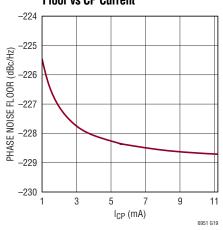

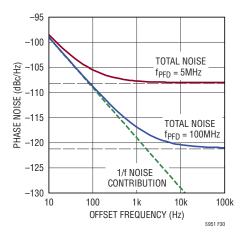

| L <sub>NORM</sub> | Normalized In-Band Phase Noise Floor                                                                                                                                 | I <sub>CP</sub> = 11.2mA (Notes 8, 9, 10)                                 | -229    |     | dBc/Hz            |

| L <sub>1/f</sub>  | Normalized In-Band 1/f Phase Noise                                                                                                                                   | I <sub>CP</sub> = 11.2mA (Notes 8, 11)                                    | -277    |     | dBc/Hz            |

|                   | In-Band Phase Noise Floor                                                                                                                                            | (Notes 8, 9, 10, 13)                                                      | -134    |     | dBc/Hz            |

|                   | Integrated Phase Noise from 100Hz to 40MHz                                                                                                                           | (Notes 9, 13)                                                             | 0.015   |     | °RMS              |

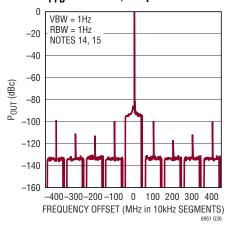

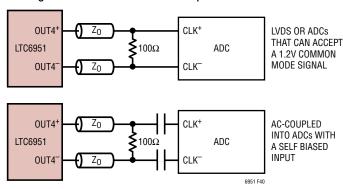

|                   | Spurious                                                                                                                                                             | f <sub>OFFSET</sub> = f <sub>PFD</sub> , PLL Locked (Notes 9, 13, 14, 15) | -95     |     | dBc               |

#### **ELECTRICAL CHARACTERISTICS**

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** The LTC6951IUHF and LTC6951IUHF-1 are guaranteed to meet specified performance limits over the full operating junction temperature range of –40°C to 105°C. Under maximum operating conditions, air flow or heat sinking may be required to maintain a junction temperature of 105°C or lower. It is strongly recommended that the Exposed Pad (Pin 41) be soldered directly to the ground plane with an array of thermal vias as described in the Applications Information section.

**Note 3:** Valid for  $1.50V \le V(TUNE) \le 2.85V$  with part calibrated after a power cycle or software power-on-reset (POR).

Note 4: Based on characterization.

**Note 5:** For 1.4V < V(CP) < 3.0V.

**Note 6:** Measurement requires RAO = 1 with SR = 1 at SYNC rising edge and SN = 1 at SYNC falling edge. REF $^+$  is a CMOS level signal with a 1ns rise time and the measurement point at the 50% crossing. SYNC is a CMOS level signal with a 1ns rise and fall time. For SYNC rising and SR = 1, the measurement point is 1.55V. For SYNC falling and SN = 1, the measurement point is 0.8V.

**Note 7:** Measured outside the loop bandwidth, using a narrowband loop.

**Note 8:** Measured inside the loop bandwidth with the loop locked.

**Note 9:** Reference frequency supplied by Wenzel 501-04516,  $f_{\text{RFF}} = 100 \text{MHz}$ ,  $P_{\text{RFF}} = 10 \text{dBm}$ .

**Note 10:** Output Phase Noise Floor is calculated from Normalized Phase Noise Floor by  $L_{OUT} = L_{NORM} + 10log_{10}(f_{PFD}) + 20log_{10}(f_{OUTx}/f_{PFD})$ .

**Note 11:** Output 1/f Noise is calculated from Normalized 1/f Phase Noise by  $L_{OUT(1/f)} = L_{1/f} + 20log_{10}(f_{OUTx}) - 10log_{10}(f_{OFFSET})$ .

**Note 12:**  $I_{CP} = 11.2 \text{mA}$ ,  $f_{PFD} = 100 \text{MHz}$ , FILT = 0, Loop BW = 340 kHz

Note 13:  $I_{CP}$  = 11.2mA,  $f_{PFD}$  = 100MHz, FILT = 0, Loop BW = 340kHz;  $f_{OUTO}$  = 500MHz,  $f_{VCO}$  = 4.0GHz.

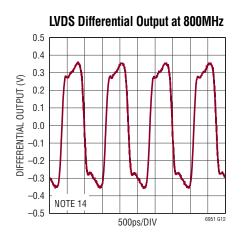

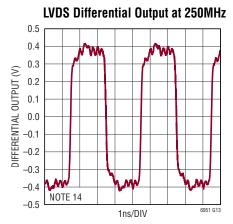

Note 14: Measured using DC2248A.

**Note 15:** Measured using differential LTC6951 outputs driving LTC6954. LTC6954 provides differential to single-ended conversion for rejection of common mode spurious signals. See the Applications Information section for details.

**Note 16:** When P = 2.5 or 3.5 and Mx = 1, a subharmonic of approximately -45 dBc to -25 dBc is generated at the output at  $f_{OUT}/2$ . While most applications are not affected by this spur, some, such as ADC and DAC sampling, are degraded. For applications sensitive to subharmonic spurs, these settings are not recommended unless the output frequency is further divided by at least 2 (i.e. ADC clock divider).

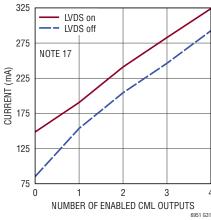

Note 17: Each output can be individually powered down by setting the output's MCx[1:0] bits to 3. See Tables 16 and 17.

# TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25^{\circ}C$ . $V_{REF}^{+} = V_{OUT}^{+} = V_{D}^{+} = V_{RF}^{+} = 3.3V$ , $V_{CP}^{+} = V_{VCO}^{+} = 5V$ , Unless otherwise noted.

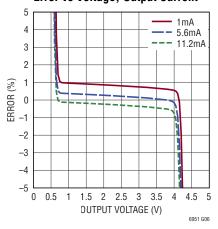

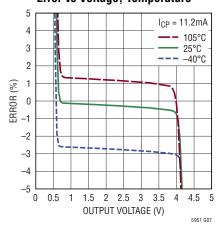

**Charge Pump Sink Current Error** vs Voltage, Output Current

**Charge Pump Sink Current Error** vs Temperature

#### **Charge Pump Source Current** Error vs Voltage, Output Current

#### **Charge Pump Source Current** Error vs Voltage, Temperature

6951fa

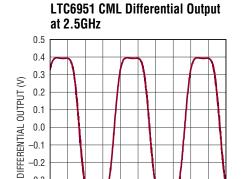

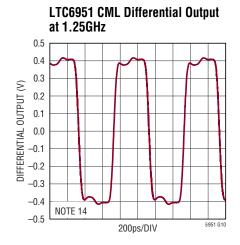

## TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25^{\circ}C$ . $V_{REF}^+ = V_{OUT}^+ = V_D^+ = V_{RF}^+ = 3.3V$ , $V_{CP}^+ = V_{VCO}^+ = 5V$ , Unless otherwise noted.

-0.2

-0.3

-0.4

-0.5

NOTE 14

LTC6951-1 CML Differential Output at 2.7GHz 0.5 0.4 0.3 DIFFERENTIAL OUTPUT (V) 0.2 0.1 0.0 -0.1 -0.2 -0.3 -0.4NOTE 14 -0.5 100ps/DIV

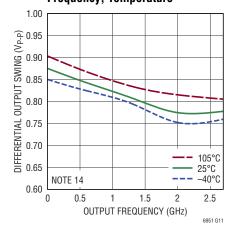

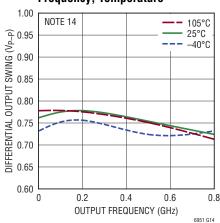

**CML Differential Output Swing vs** Frequency, Temperature

100ps/DIV

LVDS Differential Output Swing vs Frequency, Temperature

#### TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25^{\circ}C$ . $V_{REF}^{+} = V_{OUT}^{+} = V_{D}^{+} = V_{RF}^{+} = 3.3V$ ,

$V_{CP}^+ = V_{VCO}^+ = 5V$ , Unless otherwise noted.

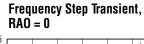

Max Calibration Time (RAO = 0)vs f<sub>PD</sub>, B Divide Value

LTC6951 VCO Tuning Sensitivity

LTC6951-1 VCO Tuning

**Normalized In-Band Phase Noise** Floor vs CP Current

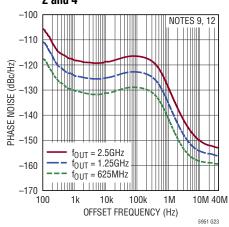

LTC6951 VCO Phase Noise at CML Outputs, P = 2, Mx = 1

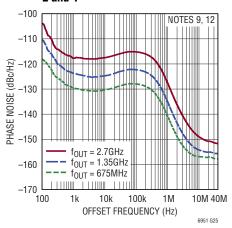

LTC6951-1 VCO Phase Noise at CML Outputs, P = 2, Mx = 1

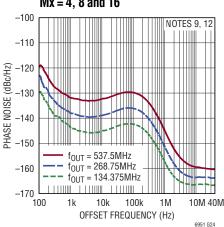

LTC6951 Phase Noise at CML Outputs,  $f_{VCO} = 4GHz$ , P = 2, Mx = 4, 8 and 16

LTC6951 Phase Noise at CML Outputs,  $f_{VCO} = 5GHz$ , P = 2, Mx = 1, 2 and 4

LTC6951-1 Phase Noise at CML Outputs,  $f_{VCO} = 4.3GHz$ , P = 2, Mx = 4, 8 and 16

6951fa

## TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25^{\circ}C$ . $V_{REF}^{+} = V_{OUT}^{+} = V_{D}^{+} = V_{RF}^{+} = 3.3V$ , $V_{CP}^{+} = V_{VCO}^{+} = 5V$ , Unless otherwise noted.

LTC6951-1 Phase Noise at CML Outputs,  $f_{VCO} = 5.4GHz$ , P = 2, Mx = 1, 2 and 4

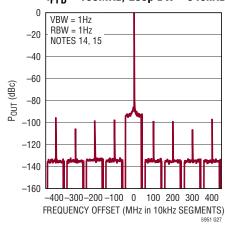

**Spurious Response**  $f_{RF}=1250M\dot{Hz},\ f_{REF}=100MHz,$  $f_{PFD} = 100MHz$ , Loop BW = 340kHz

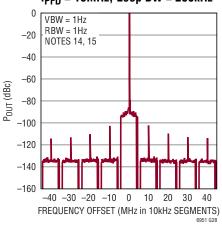

**Spurious Response**  $f_{RF}$  = 500MHz,  $f_{REF}$  = 100MHz,  $f_{PFD}$  = 100MHz, Loop BW = 340kHz

**Spurious Response**  $f_{RF} = 500MHz$ ,  $f_{REF} = 100MHz$ ,  $f_{PFD} = 10MHz$ , Loop BW = 290kHz

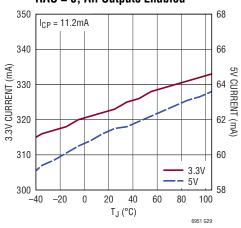

**Supply Current vs Temperature** RAO = 0, All Outputs Enabled

V<sub>OUT</sub>+ Supply Current per Output vs MCx Value

3.3V Supply Current vs **Number of Enabled CML Outputs**

Part to Part Skew, CML Outputs,

6951fa

#### PIN FUNCTIONS

$V_{OUT}^+$ ,  $V_D^+$  (Pins 1, 4, 7, 10, 13, 16): 3.15V to 3.45V Positive Supply Pins for Output Dividers, SYNC Function and Serial Port. Each pin should be separately bypassed directly to the ground plane using a 0.01µF ceramic capacitor as close to the pin as possible.  $V_{OUT}^+$ ,  $V_D^+$ ,  $V_{RF}^+$ , and  $V_{RFF}^+$  must all be at the same voltage.

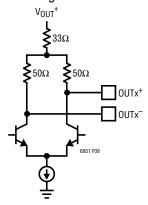

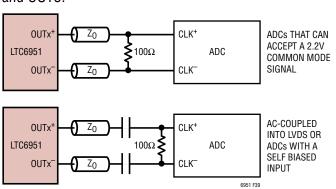

**OUT2**<sup>-</sup>, **OUT2**<sup>+</sup> (**Pins 2, 3**): 2.5V CML Output Signals. The M2 output divider is buffered and presented differentially on these pins. The outputs are connected with  $50\Omega$  (typical) pull-up resistors tied to an internal resistive common mode point. The far end of the transmission line is typically terminated with  $100\Omega$  connected across the outputs. See the Operation and Applications Information section for more details.

**OUT1**<sup>-</sup>, **OUT1**<sup>+</sup> (**Pins 5, 6**): 2.5V CML Output Signals. The M1 output divider is buffered and presented differentially on these pins. The outputs are connected with  $50\Omega$  (typical) pull-up resistors tied to an internal resistive common mode point. The far end of the transmission line is typically terminated with  $100\Omega$  connected across the outputs. See the Operation and Applications Information section for more details.

**OUTO**<sup>-</sup>, **OUTO**<sup>+</sup> (**Pins 8, 9**): 2.5V CML Output Signals. The M0 output divider is buffered and presented differentially on these pins. The outputs are connected with  $50\Omega$  (typical) pull-up resistors tied to an internal resistive common mode point. The far end of the transmission line is typically terminated with  $100\Omega$  connected across the outputs. See the Operation and Applications Information section for more details.

**OUT3**<sup>-</sup>, **OUT3**<sup>+</sup> (**Pins 11**, **12**): 2.5V CML Output Signals. The M3 output divider is buffered and presented differentially on these pins. The outputs are connected with  $50\Omega$  (typical) pull-up resistors tied to an internal resistive common mode point. The far end of the transmission line is typically terminated with  $100\Omega$  connected across the outputs. See the Operation and Applications Information section for more details.

**OUT4**<sup>-</sup>, **OUT4**<sup>+</sup> (**Pins 14, 15**): LVDS Output Signals. The M4 output divider is buffered and presented differentially on these pins. The far end of the transmission line is typically terminated with  $100\Omega$  connected across the outputs. See the Operation and Applications Information section for more details.

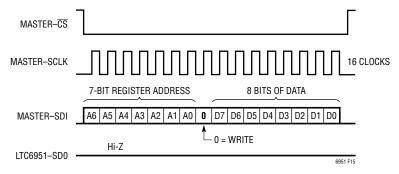

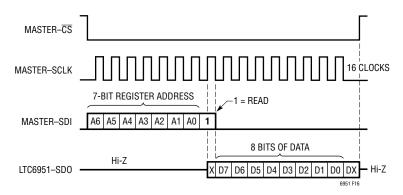

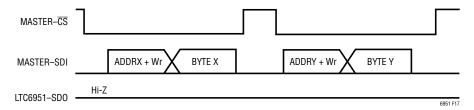

**CS** (Pin 17): Serial Port Chip Select. This CMOS input initiates a serial port communication burst when driven low, ending the burst when driven back high. See the Operation section for more details.

**SCLK (Pin 18):** Serial Port Clock. This CMOS input clocks serial port input data on its rising edge. See the Operation section for more details.

**SDI (Pin 19):** Serial Port Data Input. The serial port uses this CMOS input for data. See the Operation section for more details.

**SDO** (Pin 20): Serial Port Data Output. This CMOS three-state output presents data from the serial port during a read communication burst. Optionally attach a resistor of  $> 200 k\Omega$  to GND to prevent a floating output. See the Applications Information section for more details.

$V_{RF}^+$  (Pin 21): 3.15V to 3.45V Positive Supply Pin for RF Circuitry. This pin should be bypassed directly to the ground plane using a  $0.01\mu F$  ceramic capacitor as close to the pin as possible.  $V_{OUT}^+$ ,  $V_{D}^+$ ,  $V_{RF}^+$ , and  $V_{REF}^+$  must all be at the same voltage.

**BB (Pin 22):** RF Reference Bypass. This output has a 6.5k resistance and must be bypassed with a  $0.47\mu$ F ceramic capacitor to GND. Do not couple this pin to any other signal.

**TUNE (Pin 23):** VCO Tuning Input. This frequency control pin is normally connected to the external loop filter. See the Applications Information section for more details.

**TB** (**Pin 24**): VCO Bypass. This output has a 7k resistance and must be bypassed with a 1.0 $\mu$ F ceramic capacitor to GND. It is normally connected to CM<sub>A</sub>, CM<sub>B</sub>, and CM<sub>C</sub> with a short trace. Do not couple this pin to any other signal.

LINEAR TECHNOLOGY

#### PIN FUNCTIONS

**GND** (Pins 25, 29, Exposed Pad Pin 41): Negative Power Supply (Ground). These pins should be tied directly to the ground plane with multiple vias for each pin. The package exposed pad must be soldered directly to the PCB land. The PCB land pattern should have multiple thermal vias to the ground plane for both low ground inductance and also low thermal resistance.

$CM_C$ ,  $CM_B$ ,  $CM_A$  (Pins 26, 27, 28): VCO Bias Inputs. These inputs are normally connected to TB with a short trace and bypassed with a 1µF ceramic capacitor to GND. Do not couple these pins to any other signal. For best phase noise performance, DO NOT place a trace between these pads underneath the package.

**BVCO (Pin 30):** VCO Bypass Pin. This output must be bypassed with a 1.0µF ceramic capacitor to GND. Do not couple this pin to any other signal.

$V_{VCO}^+$  (Pin 31): 4.75V to 5.25V Positive Supply Pin for VCO Circuitry. This pin should be bypassed directly to the ground plane using a 0.01µF ceramic capacitor as close to the pin as possible.

**GND** (Pins 32, 40): Negative Power Supply (Ground). These pins are attached directly to the Die Attach Paddle (DAP) and should be tied directly to the ground plane.

$V_{CP}^+$  (Pin 33): 4.2V to 5.25V Positive Supply Pin for Charge Pump Circuitry. This pin should be bypassed directly to the ground plane using two ceramic capacitors of 1μF and 0.01μF as close to the pin as possible. Additionally, a 10Ω resistor should be added in series with the 5V power supply to reduce switching noise. The resistor should be placed between the 5V supply rail and the two ceramic capacitors.

**CP (Pin 34):** Charge Pump Output. This bidirectional current output is normally connected to the external loop filter. See the Applications Information section for more details.

$V_{REF}^+$  (Pin 35): 3.15V to 3.45V Positive Supply Pin for Reference Input Circuitry. This pin should be bypassed directly to the ground plane using a 0.1μF ceramic capacitor as close to the pin as possible.  $V_{OUT}^+$ ,  $V_{D}^+$ ,  $V_{RF}^+$ , and  $V_{REF}^+$  must all be at the same voltage.

**REF**<sup>-</sup>, **REF**<sup>+</sup> (**Pins 36, 37**): Reference Input Signals. This differential input is buffered with a low noise amplifier, which feeds the reference divider. They are self-biased and must be AC-coupled with  $1\mu F$  capacitors. If used single-ended with  $V(REF^+) \le 2.7V_{P-P}$ , bypass REF<sup>-</sup> to GND with a  $1\mu F$  capacitor. If used single-ended with  $V(REF^+) > 2.7V_{P-P}$ , bypass REF<sup>-</sup> to GND with a 47pF capacitor.

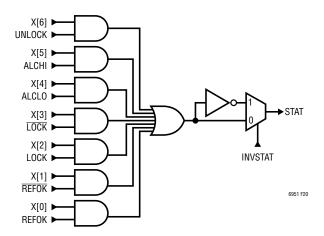

**STAT (Pin 38):** Status Output. This signal is a configurable logical OR combination of the UNLOCK, ALCHI, ALCLO, LOCK, LOCK, REFOK, and REFOK status bits, programmable via the STATUS register. See the Operation section for more details.

**SYNC (Pin 39):** Synchronization Input. This CMOS input stops the output dividers when driven high and initiates synchronization when driven back low when enabled for each output. When using the SSYNC software synchronization bit, the SYNC pin must be held at a logic low state. See the Operation and Applications Information section for more details.

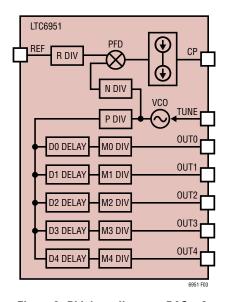

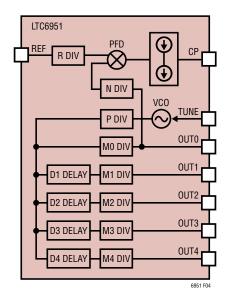

#### **BLOCK DIAGRAM**

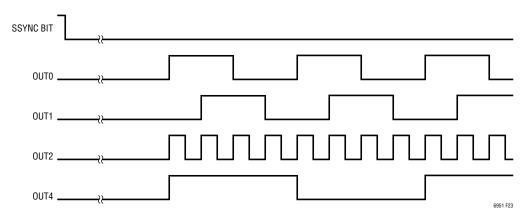

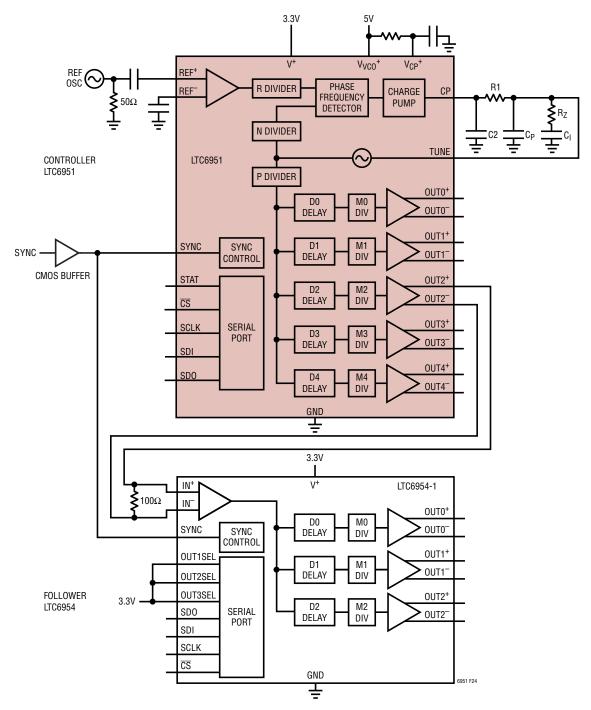

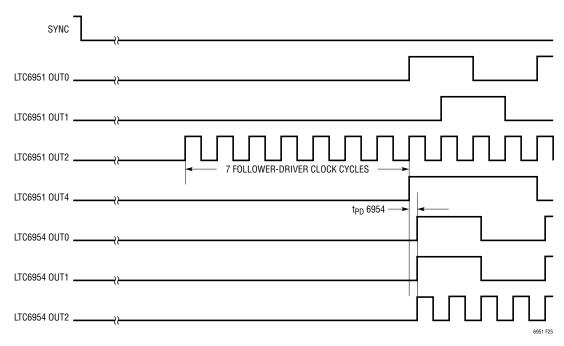

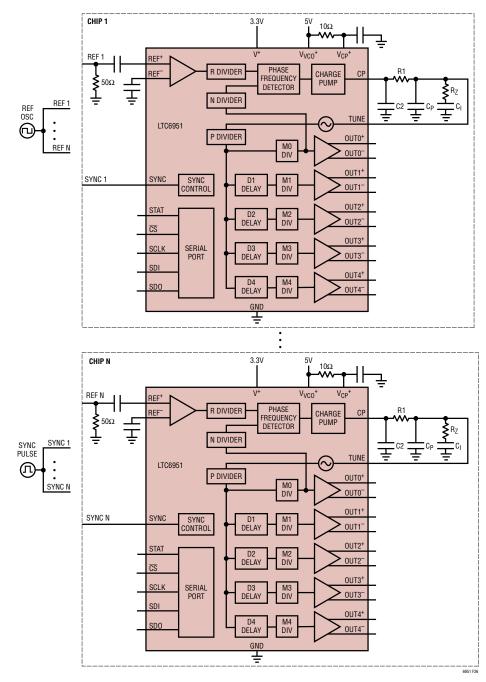

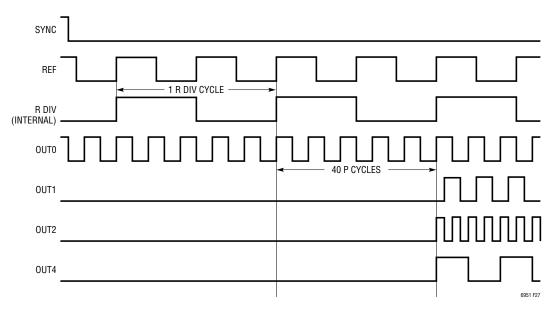

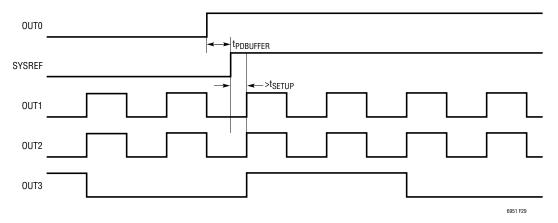

#### TIMING DIAGRAMS

# Output Skews OUT0<sup>-</sup> OUT1<sup>-</sup> OUT1<sup>+</sup> OUT2<sup>-</sup> OUT2<sup>+</sup> OUT3<sup>+</sup> OUT3<sup>+</sup> OUT4<sup>-</sup> OUT4<sup>+</sup> OUT4<sup>+</sup> OUT4<sup>+</sup> OUT4<sup>+</sup> OUT4<sup>+</sup> OUT4<sup>-</sup> OUT4<sup>-</sup> OUT4<sup>-</sup> OUT4<sup>-</sup> OUT4<sup>-</sup> OUT4<sup>-</sup> OUT4<sup>+</sup> OUT4<sup>-</sup> OUT4<sup>-</sup>

#### **Differential CML Rise/Fall Times**

#### Differential LVDS Rise/Fall Times

#### **OPERATION**

The LTC6951 is a high-performance integer-N PLL, complete with a low noise VCO. Its multi-output clock generator incorporates Linear Technology's proprietary EZSync and ParallelSync standards, allowing synchronization across multiple outputs and multiple chips. The device is able to achieve superior integrated jitter performance by the combination of its extremely low in-band phase noise and excellent VCO noise characteristics.

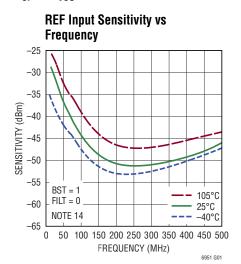

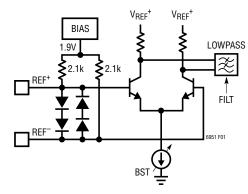

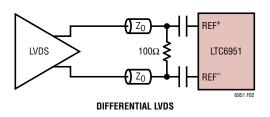

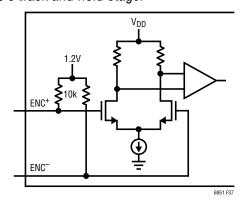

#### REFERENCE INPUT BUFFER

The PLL's reference frequency is applied differentially on pins REF+ and REF−. These high-impedance inputs are self-biased and must be AC-coupled with  $1\mu$ F capacitors (see Figure 1 for a simplified schematic). Alternatively, the inputs may be used single-ended by applying the reference frequency at REF+ and bypassing REF− to GND with a  $1\mu$ F capacitor. If the single-ended signal is greater than  $2.7V_{P-P}$ , then use a 47pF capacitor for the GND bypass.

A high quality signal must be applied to the REF $^{\pm}$  inputs as they provide the frequency reference to the entire PLL. To achieve the part's in-band phase noise performance, apply a sine wave signal of at least 6dBm into  $50\Omega$ , or a

Figure 1. Simplified REF Interface Schematic

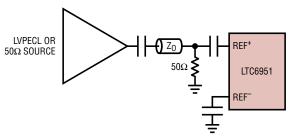

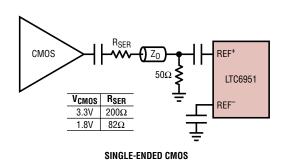

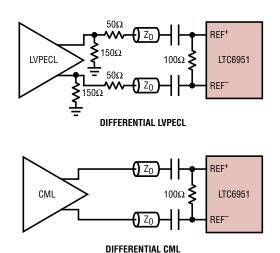

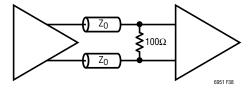

square wave of at least  $0.5V_{P-P}$  with slew rate of at least  $20V/\mu s$ . Figure 2 shows recommended interfaces for different reference types.

Additional options are available through serial port register h03 to further refine the application. Bit FILT controls the reference input buffer's low-pass filter, and should be set for sine wave signals based upon  $f_{REF}$  to limit the reference's wideband noise. The FILT bit must be set correctly to reach the  $L_{NORM}$  normalized in-band phase noise floor. See Table 1 for recommended settings. Square wave inputs will have FILT set to "0".

SINGLE-ENDED LVPECL OR  $50\Omega$  Source

Figure 2. Common Reference Input Interface Configurations. All  $Z_0$  Signal Traces Are  $50\Omega$  Transmission Lines and All Caps Are  $1\mu F$

Table 1. FILT Programming

| FILT | Sine Wave f <sub>REF</sub> | Square Wave f <sub>REF</sub> |

|------|----------------------------|------------------------------|

| 1    | <20MHz                     | N/A                          |

| 0    | ≥20MHz                     | All f <sub>REF</sub>         |

The BST bit should be set based upon the input signal level to prevent the reference input buffer from saturating. The BST programming is the same whether the input is a sine wave or a square wave. See Table 2 for recommended settings and the Applications Information section for programming examples.

**Table 2. BST Programming**

| BST | V <sub>REF</sub>     |

|-----|----------------------|

| 1   | <1.6V <sub>P-P</sub> |

| 0   | ≥1.6V <sub>P-P</sub> |

#### **Peak Detector**

A reference input peak detection circuit is provided on the REF± inputs to detect the presence of a reference signal and provides the REFOK and REFOK status flags available through both the STAT output and serial port register h00. REFOK is the logical inverse of REFOK. The circuit has hysteresis to prevent the REFOK flag from chattering at the detection threshold. The reference peak detector may be powered-down using the PDREFPK bit found in register h02.

The peak detector approximates an RMS detector, therefore sine and square wave inputs will give different detection thresholds by a factor of  $4/\pi$ . See Table 3 for REFOK detection values.

Table 3. REFOK, REFOK Status Output vs REF Input

| REFOK | REFOK | Sine Wave f <sub>REF</sub> | Square Wave f <sub>REF</sub> |

|-------|-------|----------------------------|------------------------------|

| 1     | 0     | ≥350mV <sub>P-P</sub>      | $\geq 275 \text{mV}_{P-P}$   |

| 0     | 1     | <100mV <sub>P-P</sub>      | <75mV <sub>P-P</sub>         |

LINEAD TECHNOLOGY

#### REFERENCE ALIGNED OUTPUT (RAO)

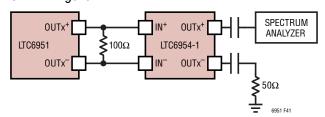

The RAO bit (register h03) controls the fundamental configuration of the PLL. Figure 3 shows the PLL loop diagram with bit RAO set to "0", which is the power-up default. All five outputs can be synchronized and delayed relative to each other, but will not be aligned to the Reference input. Systems needing alignment to the Reference input either on an individual basis or across multiple LTC6951s can set RAO to "1" to have the PLL loop diagram as shown in Figure 4. The P and MO dividers are now part of the overall feedback loop. Table 4 describes the differences in the PLL feedback elements versus the RAO bit setting. Only when the P and MO dividers are in the feedback loop can the output rising edges be coincident with the N divider output and by inference the R divider output.

When RAO is set to a "1", bits SR and SN become active and allow known and repeatable latency to the outputs in addition to known alignment to the Reference input. Figure 5 shows the operation of the SR bit and Figure 11 shows the operation of the SN bit. Table 5 is a brief description of the SR and SN functions. See the ParallelSync Multi-Chip Synchronization Example in the Applications Information section for a programming example and output timing diagrams of the RAO mode.

**Table 4. RAO Programming**

| RA0 | PLL FEEDBACK ELEMENTS |

|-----|-----------------------|

| 0   | N Divider             |

| 1   | N, P, M0 Dividers     |

Table 5. SN and SR Function Description

| RAO | SN | SR | Description                                                                                    |  |  |  |

|-----|----|----|------------------------------------------------------------------------------------------------|--|--|--|

| 0   | NA | NA | Unknown phase relationship from REF input to outputs, EZSync timing.                           |  |  |  |

| 1   | 0  | 0  | Outputs phase aligned to REF input, unknown SYNC to output latency, EZSync timing.             |  |  |  |

| 1   | 1  | 1  | Outputs phase aligned to REF input, known SYNC to output latency, critical SYNC to REF timing. |  |  |  |

Figure 3. PLL loop diagram, RAO = 0

Figure 4. PLL loop diagram, RAO = 1

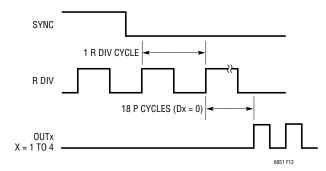

#### REFERENCE DIVIDER (R)

A 6-bit divider is used to reduce the frequency seen at the PFD. Its divide ratio R may be set to any integer from 1 to 63. Use the RD[5:0] bits found in register h05 to directly program the R divide ratio. See the Applications Information section for the relationship between R and the  $f_{REF}$ ,  $f_{PED}$ ,  $f_{VCO}$  and  $f_{OUTx}$  frequencies.

A mode to provide synchronization of the Reference inputs to the R divider output (R  $\geq$  2) using the SYNC pin input rising edge is enabled when bits RAO in register h03 and SR in register h0A are set to "1". The SYNC pin rising edge must meet setup and hold timing to the rising edge of the Reference input. See Figure 5 for the timing relationships between the Reference input, SYNC and the R divider output. Note that changing the R divider output edge timing will force the PLL to lose phase lock but will return to normal operation after several loop time constants. See Reference Signal and Sync Timing for SR and SN Modes in the Applications Information section for the timing requirements of SYNC to REF in this mode.

Figure 5. SYNC to REF timing (RAO = SR = 1)

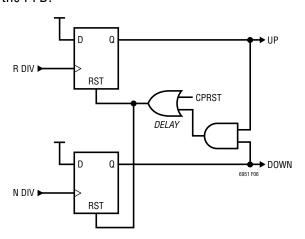

#### PHASE/FREQUENCY DETECTOR (PFD)

The phase/frequency detector (PFD), in conjunction with the charge pump, produces source and sink current pulses proportional to the phase difference between the outputs of the R and N dividers. This action provides the necessary feedback to phase-lock the loop, forcing a phase alignment at the PFD's inputs. The PFD may be disabled with

the CPRST bit which prevents UP and DOWN pulses from being produced. See Figure 6 for a simplified schematic of the PFD.

Figure 6. Simplified PFD Schematic

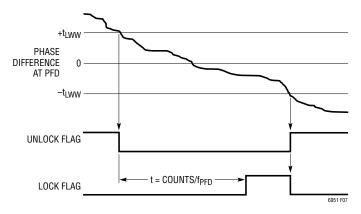

#### **LOCK INDICATOR**

The lock indicator uses internal signals from the PFD to measure phase coincidence between the R and N divider output signals. It is enabled by programming LKCT[1:0] in the serial port register h04 (see Table 7), and produces LOCK,  $\overline{LOCK}$  and UNLOCK status flags, available through both the STAT output and serial port register h00.  $\overline{LOCK}$  is the logical inverse of LOCK.

Note that f<sub>REF</sub> must be present for the LOCK and UNLOCK flags to properly assert and clear.

The user sets the phase difference lock window time  $t_{LWW}$  for a valid LOCK condition with the LKWIN bit found in register h04. Table 6 contains recommended settings for different  $f_{PFD}$  frequencies. See the Applications Information section for examples.

Table 6. LKWIN Programming

| LKWIN | t <sub>LWW</sub> | f <sub>PFD</sub> |

|-------|------------------|------------------|

| 0     | 5.0ns            | >4.7MHz          |

| 1     | 10.7ns           | ≤4.7MHz          |

The PFD phase difference must be less than  $t_{LWW}$  for the COUNTS number of successive counts before the lock indicator asserts the LOCK flag. The LKCT[1:0] bits are used to set COUNTS depending upon the application. Set LKCT[1:0] = 0 to disable the lock indicator. See Table 7 for LKCT[1:0] programming and the Applications Information section for examples.

Table 7. LKCT[1:0] Programming

| LKCT[1:0] | COUNTS                  |

|-----------|-------------------------|

| 0         | Lock Indicator Disabled |

| 1         | 32                      |

| 2         | 256                     |

| 3         | 2048                    |

When the PFD phase difference is greater than  $t_{LWW}$ , the lock indicator immediately asserts the UNLOCK status flag and clears the LOCK flag, indicating an out-of-lock condition. The UNLOCK flag is immediately de-asserted when the phase difference is less than  $t_{LWW}$ . See Figure 7 below for more details.

Figure 7. UNLOCK and LOCK Timing

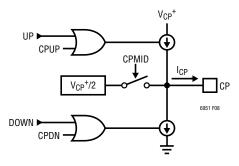

#### **CHARGE PUMP (CP)**

The charge pump, controlled by the PFD, forces sink (DOWN) or source (UP) current pulses onto the CP pin, which should be connected to an appropriate loop filter. See Figure 8 for a simplified schematic of the charge pump.

Figure 8. Simplified Charge Pump Schematic

The output current magnitude  $I_{CP}$  may be set from 1mA to 11.2mA using the CP[2:0] bits found in serial port register h07. A larger  $I_{CP}$  can result in lower in-band noise due to the lower impedance of the loop filter components. See Table 8 for programming specifics and the Applications Information section for loop filter examples.

Table 8. CP[2:0] Programming

| Table 0. Of [2.0] I rogramming |                 |

|--------------------------------|-----------------|

| CP[2:0]                        | I <sub>CP</sub> |

| 0                              | 1.0mA           |

| 1                              | 1.4mA           |

| 2                              | 2.0mA           |

| 3                              | 2.8mA           |

| 4                              | 4.0mA           |

| 5                              | 5.6mA           |

| 6                              | 8.0mA           |

| 7                              | 11.2mA          |

|                                |                 |

#### **Charge Pump Functions**

The charge pump contains additional features to aid in system startup. See Table 9 below for a summary.

Table 9. Charge Pump Function Bit Descriptions

| BIT    | DESCRIPTION                 |

|--------|-----------------------------|

| CPDN   | Force sink current.         |

| CPMID  | Enable mid-voltage bias.    |

| CPRST  | Reset PFD, Hi-Z CP.         |

| CPUP   | Force source current.       |

| CPWIDE | Extend current pulse width. |

The CPMID bit found in register h07 enables a resistive  $V_{CP}^{+}/2$  output bias which may be used to pre-bias trouble-some loop filters into a valid voltage range. When using CPMID, it is recommended to also assert the CPRST bit, forcing a PFD reset which puts the charge pump into a Hi-Z state. Both CPMID and CPRST must be set to "0" for normal operation.

The CPUP and CPDN bits force a constant  $I_{CP}$  source or sink current, respectively, on the CP pin. The CPRST bit may also be used in conjunction with the CPUP and CPDN bits, allowing a pre-charge of the loop to a known state, if required. CPUP, CPDN, and CPRST must be set to "0" to allow the loop to lock.

The CPWIDE bit extends the charge pump output current pulse width by increasing the PFD reset path's delay value. CPWIDE is normally set to "0". Setting CPWIDE = 0 provides the best in-band phase noise performance.

#### VCO

The integrated VCO operates from 4GHz to 5GHz for the LTC6951 and 4.3GHz to 5.4GHz for the LTC6951-1. The frequency range of the VCO, coupled with the output prescaler and output divider capability, allows the LTC6951 to cover an extremely wide range of continuously selectable frequencies.

The BB and TB pins are used to bias internal VCO circuitry. The BB pin has a  $6.5 k\Omega$  output resistance and should be bypassed with a  $0.47 \mu F$  ceramic capacitor to GND, giv-

ing a time constant of 3ms. The TB pin has a  $7k\Omega$  output resistance and should be bypassed with a  $1\mu F$  ceramic capacitor to GND, resulting in a time constant of 7ms. Stable bias voltages are achieved after approximately three time constants following power-up or after deasserting the PDPLL or PDVCO bits.

#### **VCO Calibration**

The VCO must be calibrated each time its frequency is modified by any change in  $f_{REF}$ , the R divider value, or the N divider value when RAO = 0. Additionally when RAO = 1, any change in  $f_{REF}$ , the R divider value, the N divider value, the P divider value, or the M0 divider value requires VCO calibration (see the Applications Information section for the relationship between R, N, P, Mx, and the  $f_{REF}$ ,  $f_{PFD}$ ,  $f_{VCO}$ , and  $f_{OUTx}$  frequencies). The output frequency is then stable over the LTC6951's entire temperature range, regardless of the temperature at which it was calibrated, until the part is reset due to a power cycle or software power-on-reset (POR).

The output of the B divider is used to clock digital calibration circuitry as shown in the Block Diagram. The B value, programmed with bits BD[3:0], is dependent on the setting of the RAO bit. The relationship between bits BD[3:0], the B value, and  $f_{PFD}$  for RAO = 0 is shown in Table 10.

Table 10. BD[3:0] Programming, RAO = 0

| BD[3:0]  | B DIVIDE VALUE | f <sub>PFD</sub> (MHz) |

|----------|----------------|------------------------|

| 0        | 8              | <2.4                   |

| 1        | 12             | 2.4 to 3.6             |

| 2        | 16             | 3.6 to 4.8             |

| 3        | 24             | 4.8 to 7.2             |

| 4        | 32             | 7.2 to 9.6             |

| 5        | 48             | 9.6 to 14              |

| 6        | 64             | 14 to 19               |

| 7        | 96             | 19 to 29               |

| 8        | 128            | 29 to 38               |

| 9        | 192            | 38 to 58               |

| 10       | 256            | 58 to 77               |

| 11       | 384            | >77                    |

| 12 to 15 | Invalid        |                        |

The relationship between bits BD[3:0], the B value, and the N value for RAO = 1 is shown in Table 11.

Table 11. BD[3:0] Programming, RAO = 1

| BD[3:0]  | B DIVIDE VALUE | N DIVIDE VALUE |

|----------|----------------|----------------|

| 0        | 8              | NA             |

| 1        | 12             | 240 to 511     |

| 2        | 16             | 180 to 239     |

| 3        | 24             | 120 to 179     |

| 4        | 32             | 90 to 119      |

| 5        | 48             | 60 to 89       |

| 6        | 64             | 45 to 59       |

| 7        | 96             | 30 to 44       |

| 8        | 128            | 23 to 29       |

| 9        | 192            | 12 to 22       |

| 10       | 256            | 4 to 11        |

| 11       | 384            | 2 to 3         |

| 12 to 15 | Invalid        |                |

Once the RD[5:0], ND[9:0], and BD[3:0] bits are written and the reference frequency  $f_{REF}$  is present and stable at the REF $^{\pm}$  inputs, the VCO must be calibrated by setting CAL = 1 (the bit self-clears when calibration is complete). The calibration cycle takes between 12 and 14 clocks of the B divider output with the nominal calibration time shown in Equation 1. Setting bits MCx[1:0] = 1 selectively mutes the outputs during the calibration.

$$t_{CAL} = \frac{14 \cdot B}{f_{PFD}} \tag{1}$$

Note that the  $f_{REF}$  frequency and TB and BB voltages must be stable for proper calibration. Stable bias voltages are achieved after approximately three time constants (about 25ms) following power-up.

Setting AUTOCAL = 1 causes the CAL bit to be set automatically whenever serial port registers h05 or h06 are written. When AUTOCAL is enabled and RAO = 0, there is no need for a separate register write to set the CAL bit.

When RAO = 1 the loop also uses the P and MO divide values which are located in registers h08 and h09 which when changed will not trigger the CAL bit with AUTOCAL = 1.

It is recommended to set AUTOCAL = 0 in this mode and to calibrate the VCO by setting CAL = 1 after all the appropriate registers have been written. See Table 12 for a summary of the VCO bits.

Table 12. VCO Bit Descriptions

| BIT      | DESCRIPTION                                                |

|----------|------------------------------------------------------------|

| AUTOCAL  | Calibrate VCOs whenever registers h05 and h06 are written. |

| CAL      | Start VCO calibration (auto clears).                       |

| MC0[1:0] | Setting to h1 mutes OUTO output during calibration.        |

| MC1[1:0] | Setting to h1 mutes OUT1 output during calibration.        |

| MC2[1:0] | Setting to h1 mutes OUT2 output during calibration.        |

| MC3[1:0] | Setting to h1 mutes OUT3 output during calibration.        |

| MC4[1:0] | Setting to h1 mutes OUT4 output during calibration.        |

#### VCO Automatic Level Control (ALC)

The VCO uses an internal automatic level control (ALC) algorithm to maintain an optimal amplitude on the VCO resonator, and thus optimal phase noise performance. The user has several ALC configuration and status reporting options as seen in Table 13.

Table 13. ALC Bit Descriptions

| BIT     | DESCRIPTION                                                             |

|---------|-------------------------------------------------------------------------|

| ALCCAL  | Auto enable ALC during CAL operation.                                   |

| ALCEN   | Always enable ALC (overrides ALCCAL, ALCMON, and ALCULOK).              |

| ALCHI   | ALC too high flag (resonator amplitude too high).                       |

| ALCLO   | ALC too low flag (resonator amplitude too low).                         |

| ALCMON  | Enable amplitude monitoring for status flags only; does NOT enable ALC. |

| ALCULOK | Auto enable ALC when PLL unlocked.                                      |

Changes in the internal ALC output can cause extremely small jumps in the VCO frequency. These jumps may be acceptable in some applications but not in others. Use the above table to choose when the ALC is active. The ALCHI and ALCLO flags, valid only when the ALC is active or the ALCMON bit is set, may be used to monitor the resonator amplitude.

The ALC must be allowed to operate during or after a calibration cycle. At least one of the ALCCAL, ALCEN, or ALCULOK bits must be set.

#### **VCO DIVIDER (N)**

The 10-bit N divider provides the feedback from the VCO to the PFD. The divide ratio may be programmed from 32 to 1023, when bit RAO = 0. The divide ratio may be programmed from 2 to 511, when bit RAO = 1. Use the ND[9:0] bits found in registers h05 and h06 to directly program the N divide ratio. See the Applications Information section for the relationship between N and the  $f_{REF}$ ,  $f_{PFD}$ ,  $f_{VCO}$  and  $f_{OUTx}$  frequencies.

#### **VCO PRESCALER (P)**

The P divider reduces the VCO frequency and distributes it to the five output dividers. The available divide ratios of 2, 2.5, 3, 3.5 and 4, when coupled with the VCO frequency range, allow the P divider output to cover more than an octave of frequency. See Table 14 for programming specifics and the Applications Information section for the relationship between P and the  $f_{REF}$ ,  $f_{PFD}$ ,  $f_{VCO}$  and  $f_{OUTx}$  frequencies.

Table 14. PD[2:0] Programming

| PD[2:0] | P       |

|---------|---------|

| 0       | 2       |

| 1       | 2.5     |

| 2       | 3       |

| 3       | 3.5     |

| 4       | 4       |

| 5 to 7  | Invalid |

|         |         |

#### OUTPUT DIVIDERS (MO, M1, M2, M3, M4)

The five independent output dividers are driven by the P divider. All settings of  $Mx \ge 2$  with any P value or Mx = 1 with P = 2, 3, or 4 provide a 50% duty cycle at the output. Setting Mx = 1 with P = 2.5 or 3.5 is allowable, but will produce a signal with a non-50% duty cycle (40% and 57%, respectively) and a large subharmonic spurious output. In systems where the LTC6951 output drives into a frequency divider of at least 2 (as in some ADCs), the subharmonic spur will be removed and the duty cycle will go to 50% at the frequency divider output.

The relationship between the Mx value and the MDx[3:0] bits is shown in Table 15. Unused dividers can be powered