# 4GHz Ultra-Low Bias Current FET Input Op Amp

#### **FEATURES**

- Gain Bandwidth Product: 4GHz

- Low Input Bias Current:

- ±3fA Tvp. Room Temperature

- 4pA Max at 125°C

- Current Noise (100kHz): 7fA/√Hz

- Voltage Noise (1MHz): 4.0nV/√Hz

- Extremely Low C<sub>IN</sub> 0.45pF

- Rail-to-Rail Output

- A<sub>V</sub> ≥10

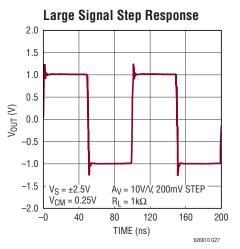

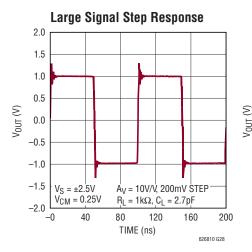

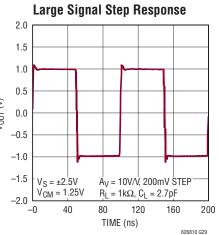

- Slew Rate: +1500V/µs, -1000V/µs

- Supply Range: 3.1V to 5.25V

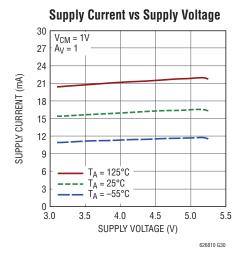

- Quiescent Current: 16.5mA

- Operating Temp Range: -40°C to 125°C

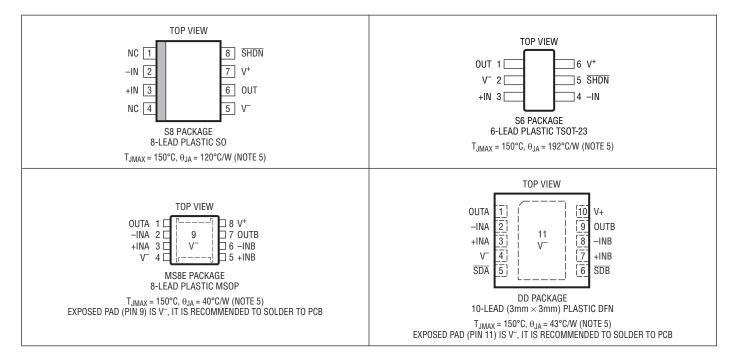

- Single in 8-Lead SO-8, 6-Lead TSOT-23 Packages

- Dual in 8-Lead MS8, 3mm × 3mm 10-Lead DFN 10 Packages

#### **APPLICATIONS**

- Transimpedance Amplifiers

- ADC Drivers

- Photomultiplier Tube Post-Amplifier

- Low I<sub>BIAS</sub> Circuits

#### DESCRIPTION

The LTC®6268-10/LTC6269-10 is a single/dual 4GHz FET-input operational amplifier with extremely low input bias current and low input capacitance. It also features low input-referred current noise and voltage noise making it an ideal choice for high speed transimpedance amplifiers, and high-impedance sensor amplifiers. It is a decompensated op amp that is gain-of-10 stable.

It operates on 3.1V to 5.25V supply and consumes 16.5mA per amplifier. A shutdown feature can be used to lower power consumption when the amplifier is not in use.

The LTC6268-10 single op amp is available in 8-lead SOIC and 6-lead SOT-23 packages. The SOIC package includes two unconnected pins which can be used to create an input pin guard ring to protect against board leakage currents. The LTC6269-10 dual op amp is available in 8-lead MSOP with exposed pad and  $3\text{mm} \times 3\text{mm}$  10-lead DFN packages. They are fully specified over the  $-40^{\circ}\text{C}$  to  $85^{\circ}\text{C}$  and the  $-40^{\circ}\text{C}$  to  $125^{\circ}\text{C}$  temperature ranges.

T, LT, LTC, LTM, Linear Technology and the Linear logo are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.

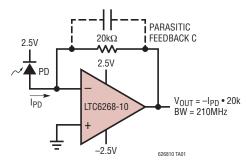

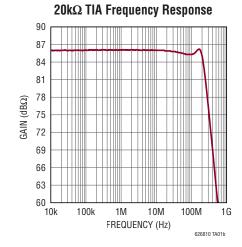

#### TYPICAL APPLICATION

$20k\Omega$  Gain 210MHz Transimpedance Amplifier

PD = OSI OPTOELECTRONICS, FCI-125G-006

#### **ABSOLUTE MAXIMUM RATINGS**

(Note 1)

| Supply Voltage V <sup>+</sup> to V <sup>-</sup> | 5.5V                               |

|-------------------------------------------------|------------------------------------|

| Input Voltage                                   | $1.V^{-} - 0.2V$ to $V^{+} + 0.2V$ |

| Input Current (+IN, -IN) (Note 2)               | ±1mA                               |

| Input Current (SHDN)                            | ±1mA                               |

| Output Current (I <sub>OUT</sub> ) (Note 8, 9)  | 135mA                              |

| <b>Output Short-Circuit Duration (Not</b>       |                                    |

| Operating Temperature Range                     | ,                                  |

| LTC6268-10I/LTC6269-10I                         | 40°C to 85°C                       |

| LTC6268-10H/LTC6269-10H                         | 40°C to 125°C                      |

| Specified Temperature Range (Note 4 | .)             |

|-------------------------------------|----------------|

| LTC6268-10I/LTC6269-10I             | 40°C to 85°C   |

| LTC6268-10H/LTC6269-10H             | 40°C to 125°C  |

| Maximum Junction Temperature        | 150°C          |

| Storage Temperature Range           | –65°C to 150°C |

| Lead Temperature S8, S6 and         |                |

| MS8E (Soldering, 10 sec)            | 300°C          |

|                                     |                |

### PIN CONFIGURATION

#### ORDER INFORMATION

| LEAD FREE FINISH     | TAPE AND REEL         | PART MARKING* | PACKAGE DESCRIPTION    | SPECIFIED TEMPERATURE RANGE |

|----------------------|-----------------------|---------------|------------------------|-----------------------------|

| LTC6268IS6-10#TRMPBF | LTC6268IS6-10#TRPBF   | LTGQT         | 6-Lead Plastic TSOT-23 | -40°C to 85°C               |

| LTC6268HS6-10#TRMPBF | LTC6268HS6-10#TRPBF   | LTGQT         | 6-Lead Plastic TSOT-23 | -40°C to 125°C              |

| LTC6268IS8-10#PBF    | LTC6268IS8-10#TRPBF   | 626810        | 8-Lead Plastic SOIC    | -40°C to 85°C               |

| LTC6268HS8-10#PBF    | LTC6268HS8-10#TRPBF   | 626810        | 8-Lead Plastic SOIC    | -40°C to 125°C              |

| LTC6269IMS8E-10#PBF  | LTC6269IMS8E-10#TRPBF | LTGRM         | 8-Lead Plastic MSOP    | -40°C to 85°C               |

| LTC6269HMS8E-10#PBF  | LTC6269HMS8E-10#TRPBF | LTGRM         | 8-Lead Plastic MSOP    | -40°C to 125°C              |

| LTC6269IDD-10#PBF    | LTC6269IDD-10#TRPBF   | LGRK          | 10-Lead Plastic DD     | -40°C to 85°C               |

| LTC6269HDD-10#PBF    | LTC6269HDD-10#TRPBF   | LGRK          | 10-Lead Plastic DD     | -40°C to 125°C              |

$Consult\ LTC\ Marketing\ for\ parts\ specified\ with\ wider\ operating\ temperature\ ranges.\ {}^*The\ temperature\ grade\ is\ identified\ by\ a\ label\ on\ the\ shipping\ container.$

For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

# **5.0V ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes specifications that apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ , $V_{SUPPLY} = 5.0V$ (V<sup>+</sup> = 5V, V<sup>-</sup> = 0V, $V_{CM} = mid$ -supply), $R_L = 1k\Omega$ , $V_{\overline{SHDN}}$ is unconnected.

| SYMBOL             | PARAMETER                                            | CONDITIONS                                                                    |   | MIN               | TYP   | MAX            | UNITS             |

|--------------------|------------------------------------------------------|-------------------------------------------------------------------------------|---|-------------------|-------|----------------|-------------------|

| V <sub>OS</sub>    | Input Offset Voltage                                 | V <sub>CM</sub> = 2.75V                                                       | • | -0.7<br>-3        | 0.2   | 0.7<br>3       | mV<br>mV          |

|                    |                                                      | V <sub>CM</sub> = 4.0V                                                        | • | -1.0<br>-4.5      | 0.2   | 1.0<br>4.5     | mV<br>mV          |

| TC V <sub>OS</sub> | Input Offset Voltage Drift                           | V <sub>CM</sub> = 2.75V                                                       |   |                   | 4     |                | μV/°C             |

| I <sub>B</sub>     | Input Bias Current (Notes 6, 8)                      | V <sub>CM</sub> = 2.75V<br>LTC6268I-10/LTC6269I-10<br>LTC6268H-10/LTC6269H-10 | • | -20<br>-900<br>-4 | ±3    | 20<br>900<br>4 | fA<br>fA<br>pA    |

|                    |                                                      | V <sub>CM</sub> = 4.0V<br>LTC6268I-10/LTC6269I-10<br>LTC6268H-10/LTC6269H-10  | • | -20<br>-900<br>-4 | ±3    | 20<br>900<br>4 | fA<br>fA<br>pA    |

| I <sub>OS</sub>    | Input Offset Current (Notes 6, 8)                    | V <sub>CM</sub> = 2.75V<br>LTC6268I-10/LTC6269I-10<br>LTC6268H-10/LTC6269H-10 | • | -40<br>-450<br>-2 | ±6    | 40<br>450<br>2 | fA<br>fA<br>pA    |

| e <sub>n</sub>     | Input Voltage Noise Density, V <sub>CM</sub> = 2.75V | f = 1MHz                                                                      |   |                   | 4.0   |                | nV/√Hz            |

|                    | Input Voltage Noise Density, V <sub>CM</sub> = 4.0V  | f = 1MHz                                                                      |   |                   | 4.0   |                | nV/√Hz            |

|                    | Input Referred Noise Voltage                         | f = 0.1Hz to 10Hz                                                             |   |                   | 12.6  |                | μV <sub>P-P</sub> |

| in                 | Input Current Noise Density, $V_{CM} = 2.75V$        | f = 100kHz                                                                    |   |                   | 7     |                | fA/√Hz            |

|                    | Input Current Noise Density, V <sub>CM</sub> = 4.0V  | f = 100kHz                                                                    |   |                   | 7     |                | fA/√Hz            |

| R <sub>IN</sub>    | Input Resistance                                     | Differential                                                                  |   |                   | >1000 |                | GΩ                |

|                    |                                                      | Common Mode                                                                   |   |                   | >1000 |                | GΩ                |

| C <sub>IN</sub>    | Input Capacitance                                    | Differential (DC to 200MHz)                                                   |   |                   | 0.1   |                | pF                |

|                    |                                                      | Common Mode (DC to 100MHz)                                                    |   |                   | 0.45  |                | pF                |

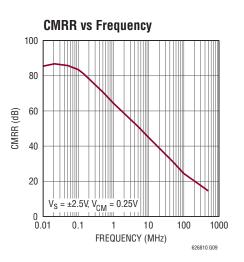

| CMRR               | Common Mode Rejection Ratio                          | V <sub>CM</sub> = 0.5V to 3.2V (PNP Side)                                     | • | 72<br>68          | 85    |                | dB<br>dB          |

|                    |                                                      | $V_{CM} = -0.1V$ to 4.5V                                                      | • | 64<br>52          | 82    |                | dB<br>dB          |

| IVR                | Input Voltage Range                                  | Guaranteed by CMRR                                                            | • | -0.1              |       | 4.5            | V                 |

# **5.0V ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes specifications that apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ , $V_{SUPPLY} = 5.0V$ (V<sup>+</sup> = 5V, V<sup>-</sup> = 0V, $V_{CM} = mid$ -supply), $R_L = 1k\Omega$ , $V_{SHDN}$ is unconnected.

| SYMBOL            | PARAMETER                                                                | CONDITIONS                                                                                                                                                      |                          |   | MIN         | TYP     | MAX         | UNITS        |

|-------------------|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|---|-------------|---------|-------------|--------------|

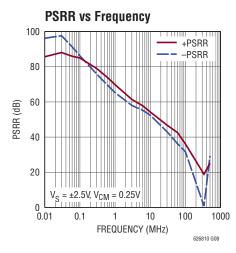

| PSRR              | Power Supply Rejection Ratio                                             | V <sub>CM</sub> = 1.0V, V <sub>SUPPLY</sub> Ranges from 3.1V to 5.25V                                                                                           |                          | • | 78<br>75    | 95      |             | dB<br>dB     |

|                   | Supply Voltage Range                                                     |                                                                                                                                                                 |                          | • | 3.1         |         | 5.25        |              |

| A <sub>V</sub>    | Open Loop Voltage Gain                                                   | $V_{OUT} = 0.5V \text{ to } 4.5V$                                                                                                                               | R <sub>LOAD</sub> = 10k  | • | 125<br>40   | 250     |             | V/mV<br>V/mV |

|                   |                                                                          |                                                                                                                                                                 | R <sub>LOAD</sub> = 100  | • | 10<br>2     | 21      |             | V/mV<br>V/mV |

| V <sub>OL</sub>   | Output Swing Low (Input Overdrive 30mV)<br>Measured from V <sup>-</sup>  | I <sub>SINK</sub> = 10mA                                                                                                                                        |                          | • |             | 80      | 140<br>200  | mV<br>mV     |

|                   |                                                                          | I <sub>SINK</sub> = 25mA                                                                                                                                        |                          | • |             | 130     | 200<br>260  | mV<br>mV     |

| V <sub>OH</sub>   | Output Swing High (Input Overdrive 30mV)<br>Measured from V <sup>+</sup> | I <sub>SOURCE</sub> = 10mA                                                                                                                                      |                          | • |             | 70      | 140<br>200  | mV<br>mV     |

|                   |                                                                          | I <sub>SOURCE</sub> = 25mA                                                                                                                                      |                          | • |             | 160     | 270<br>370  | mV<br>mV     |

| I <sub>SC</sub>   | Output Short Circuit Current (Note 9)                                    |                                                                                                                                                                 |                          | • | 60<br>40    | 90      |             | mA<br>mA     |

| Is                | Supply Current Per Amplifier                                             |                                                                                                                                                                 |                          | • | 15<br>9     | 16.5    | 18<br>25    | mA<br>mA     |

|                   | Supply Current in Shutdown<br>(Per Amplifier)                            |                                                                                                                                                                 |                          | • |             | 0.39    | 0.85<br>1.5 | mA<br>mA     |

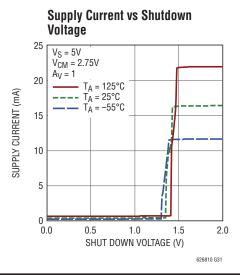

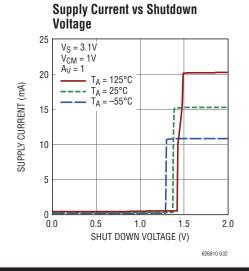

| I <sub>SHDN</sub> | Shutdown Pin Current                                                     | V <sub>SHDN</sub> = 0.75V<br>V <sub>SHDN</sub> = 1.50V                                                                                                          |                          | • | -12<br>-12  | 2<br>2  | 12<br>12    | μΑ<br>μΑ     |

| V <sub>IL</sub>   | SHDN Input Low Voltage                                                   | Disable                                                                                                                                                         |                          | • |             |         | 0.75        | V            |

| $V_{IH}$          | SHDN Input High Voltage                                                  | Enable. If SHDN is Unco                                                                                                                                         | onnected, Amp is Enabled | • | 1.5         |         |             | V            |

| t <sub>ON</sub>   | Turn On Time, Delay from SHDN Toggle to Output Reaching 90% of Target    | SHDN Toggle from 0V t                                                                                                                                           | 0 2V                     |   |             | 360     |             | ns           |

| t <sub>OFF</sub>  | Turn Off Time, Delay from SHDN Toggle to Output High Z                   | SHDN Toggle from 2V t                                                                                                                                           | 0 OV                     |   |             | 183     |             | ns           |

| GBW               | Gain-Bandwidth Product (Note 8)                                          | f = 10MHz                                                                                                                                                       |                          | • | 3500        | 4000    |             | MHz          |

| SR+               | Slew Rate+                                                               | $\begin{array}{l} A_V = 11 \; (R_F = 1000,  R_G = 100) \\ V_{OUT} = 0.5V \; to \; 4.5V, \; Measured \; 20\% \; to \; 80\%, \\ R_{LOAD} = 500\Omega \end{array}$ |                          | • | 1100<br>600 | 1500    |             | V/µs<br>V/µs |

| SR-               | Slew Rate-                                                               | $A_V = 11 \text{ (R}_F = 1000, R_G = 100)$<br>$V_{OUT} = 4.5V \text{ to } 0.5V, \text{ Measured } 80\% \text{ to } 20\%,$                                       |                          | • | 900<br>500  | 1000    |             | V/µs<br>V/µs |

| FPBW              | Full Power Bandwidth (Note 7)                                            | 4V <sub>P-P</sub>                                                                                                                                               |                          |   |             | 73      |             | MHz          |

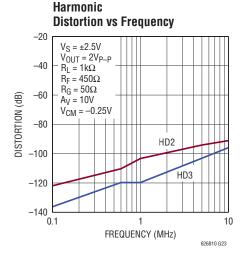

| HD                | Harmonic Distortion(HD2/HD3)                                             | $A_V$ = 10, 10MHz. $2V_{P-P}$ , $V_{CM}$ = 2.25V, $R_L$ = 1k, RF = 450 $\Omega$ , RG = 50 $\Omega$                                                              |                          |   |             | -91/-96 |             | dB           |

| I <sub>LEAK</sub> | Output Leakage Current in Shutdown                                       | $V_{\overline{S}H\overline{D}\overline{N}} = 0V, V_{OUT} = 0V$<br>$V_{\overline{S}H\overline{D}\overline{N}} = 0V, V_{OUT} = 5V$                                |                          |   |             |         | 400<br>400  | nA<br>nA     |

# **3.3V ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes specifications that apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ , $V_{SUPPLY} = 3.3V$ (V<sup>+</sup> = 3.3V, V<sup>-</sup> = 0V, $V_{CM}$ = mid-supply), $R_L = 1k\Omega$ , $V_{SHDN}$ is unconnected.

| SYMBOL                                                    | PARAMETER                                           | CONDITIONS                                                              |                                                           |   | MIN               | TYP            | MAX            | UNITS             |

|-----------------------------------------------------------|-----------------------------------------------------|-------------------------------------------------------------------------|-----------------------------------------------------------|---|-------------------|----------------|----------------|-------------------|

| V <sub>0S</sub>                                           | Input Offset Voltage                                | V <sub>CM</sub> = 1.0V                                                  |                                                           | • | -0.7<br>-3        | 0.2            | 0.7<br>3       | mV<br>mV          |

|                                                           |                                                     | V <sub>CM</sub> = 2.3V                                                  | V <sub>CM</sub> = 2.3V                                    |   | -1.0<br>-4.5      | 0.2            | 1.0<br>4.5     | mV<br>mV          |

| TC V <sub>OS</sub>                                        | Input Offset Voltage Drift                          | V <sub>CM</sub> = 1.0V                                                  |                                                           |   |                   | 4              |                | μV/C              |

| I <sub>B</sub>                                            | Input Bias Current (Notes 6, 8)                     | V <sub>CM</sub> = 1.0V<br>LTC6268I-10/LTC6269I-<br>LTC6268H-10/LTC6269H |                                                           | • | -20<br>-900<br>-4 | ±3             | 20<br>900<br>4 | fA<br>fA<br>pA    |

|                                                           |                                                     | V <sub>CM</sub> = 2.3V<br>LTC6268I-10/LTC6269I-<br>LTC6268H-10/LTC6269H |                                                           | • | -20<br>-900<br>-4 | ±3             | 20<br>900<br>4 | fA<br>fA<br>pA    |

| I <sub>OS</sub>                                           | Input Offset Current (Notes 6, 8)                   | V <sub>CM</sub> = 1.0V<br>LTC6268I-10/LTC6269I-<br>LTC6268H-10/LTC6269H |                                                           | • | -40<br>-450<br>-2 | ±6             | 40<br>450<br>2 | fA<br>fA<br>pA    |

| e <sub>n</sub>                                            | Input Voltage Noise Density, V <sub>CM</sub> =1.0V  | f = 1MHz                                                                |                                                           |   |                   | 4.0            |                | nV/√Hz            |

|                                                           | Input Voltage Noise Density, V <sub>CM</sub> = 2.3V | f = 1MHz                                                                |                                                           |   |                   | 4.0            |                | nV/√Hz            |

|                                                           | Input Referred Noise Voltage                        | f = 0.1Hz to 10Hz                                                       |                                                           |   |                   | 13.5           |                | μV <sub>P-P</sub> |

| i <sub>n</sub>                                            | Input Current Noise Density, V <sub>CM</sub> = 1.0V | f = 100kHz                                                              |                                                           |   |                   | 7              |                | fA/√Hz            |

|                                                           | Input Current Noise Density, V <sub>CM</sub> = 2.3V | f = 100kHz                                                              |                                                           |   |                   | 7              |                | fA/√Hz            |

| R <sub>IN</sub>                                           | Input Resistance                                    | Differential<br>Common Mode                                             |                                                           |   |                   | >1000<br>>1000 |                | GΩ<br>GΩ          |

| $C_{IN}$                                                  | Input Capacitance                                   |                                                                         | Differential (DC to 200MHz)<br>Common Mode (DC to 100MHz) |   |                   | 0.1<br>0.45    |                | pF<br>pF          |

| CMRR                                                      | Common Mode Rejection Ratio                         | V <sub>CM</sub> = 0.5V to 1.2V (PNF                                     | 'Side)                                                    | • | 63<br>60          | 90             |                | dB<br>dB          |

|                                                           |                                                     | $V_{CM} = -0.1V \text{ to } 2.8V \text{ (Full bounds)}$                 | II Range)                                                 | • | 60<br>50          | 77             |                | dB<br>dB          |

| IVR                                                       | Input Voltage Range                                 | Guaranteed by CMRR                                                      |                                                           | • | -0.1              |                | 2.8            | V                 |

| A <sub>V</sub>                                            | Open Loop Voltage Gain                              | V <sub>OUT</sub> = 0.5V to 2.8V                                         | R <sub>LOAD</sub> = 10k                                   | • | 80<br>40          | 200            |                | V/mV<br>V/mV      |

|                                                           |                                                     |                                                                         | R <sub>LOAD</sub> = 100                                   | • | 10<br>2           | 18             |                | V/mV<br>V/mV      |

| $V_{OL}$                                                  | Output Swing Low (Input Overdrive 30mV).            | I <sub>SINK</sub> = 10mA                                                |                                                           | • |                   | 80             | 140<br>200     | mV<br>mV          |

|                                                           | Measured from V <sup>-</sup>                        | I <sub>SINK</sub> = 25mA                                                |                                                           | • |                   | 140            | 200<br>260     | mV<br>mV          |

| V <sub>OH</sub> Output Swing High (Input Overdrive 30mV). |                                                     | I <sub>SOURCE</sub> = 10mA                                              |                                                           | • |                   | 80             | 140<br>200     | mV<br>mV          |

|                                                           | Measured from V <sup>+</sup>                        | I <sub>SOURCE</sub> = 25mA                                              |                                                           | • |                   | 170            | 270<br>370     | mV<br>mV          |

| I <sub>SC</sub>                                           | Output Short Circuit Current (Note 9)               |                                                                         |                                                           | • | 50<br>35          | 80             |                | mA<br>mA          |

| Is                                                        | Supply Current per Amplifier                        |                                                                         |                                                           | • | 14.5<br>9         | 16             | 17.5<br>25     | mA<br>mA          |

# **3.3V ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes specifications that apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ , $V_{SUPPLY} = 3.3V$ ( $V^+ = 3.3V$ , $V^- = 0V$ , $V_{CM} = mid$ -supply) $R_L = 1k\Omega$ , $V_{\overline{SHDN}}$ is unconnected.

| SYMBOL            | PARAMETER                                                             | CONDITIONS                                                                                                                                                        |   | MIN        | TYP             | MAX        | UNITS        |

|-------------------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------------|-----------------|------------|--------------|

|                   | Supply Current in Shutdown<br>(Per Amplifier)                         |                                                                                                                                                                   | • |            | 0.23            | 0.6<br>1.2 | mA<br>mA     |

| I <sub>SHDN</sub> | Shutdown Pin Current                                                  | V <sub>SHDN</sub> = 0.75V<br>V <sub>SHDN</sub> = 1.5V                                                                                                             | • | -12<br>-12 | 2<br>2          | 12<br>12   | μA<br>μA     |

| $V_{IL}$          | SHDN Input Low Voltage                                                | Disable                                                                                                                                                           | • |            |                 | 0.75       | V            |

| V <sub>IH</sub>   | SHDN Input High Voltage                                               | Enable. If SHDN is Unconnected, Amp Is Enabled                                                                                                                    | • | 1.5        |                 |            | V            |

| t <sub>ON</sub>   | Turn On Time, Delay from SHDN Toggle to Output Reaching 90% of Target | SHDN Toggle from 0V to 2V                                                                                                                                         |   |            | 750             |            | ns           |

| t <sub>OFF</sub>  | Turn Off Time, Delay from SHDN Toggle to Output High Z                | SHDN Toggle from 2V to 0V                                                                                                                                         |   |            | 201             |            | ns           |

| GBW               | Gain-Bandwidth Product (Note 8)                                       | f = 10MHz                                                                                                                                                         | • | 3500       | 4000            |            | MHz          |

| SR+               | Slew Rate+                                                            | $\label{eq:AV} \begin{cases} A_V = 11 \ (R_F = 1000,  R_G = 100), \\ V_{OUT} = 1V \ to \ 2.3V,  Measured \ 20\% \ to \ 80\%, \\ R_{LOAD} = 500\Omega \end{cases}$ | • | 800<br>600 | 1500            |            | V/µs<br>V/µs |

| SR-               | Slew Rate-                                                            | $\begin{array}{l} A_V=11 \ (R_F=1000,R_G=100),\\ V_{OUT}=1V \ to \ 2.3V, \ Measured \ 80\% \ to \ 20\%,\\ R_{L0AD}=500\Omega \end{array}$                         | • | 600<br>400 | 1000            |            | V/µs<br>V/µs |

| FPBW              | Full Power Bandwidth (Note 7)                                         | 2.3V <sub>P-P</sub>                                                                                                                                               |   |            | 105             |            | MHz          |

| HD                | Harmonic Distortion(HD2/HD3)                                          | A = 10, 10MHz. $2V_{P-P}$ , $V_{CM}$ = 1.65V, $R_L$ = 1k, $RF$ = $450\Omega$ , $RG$ = $50\Omega$                                                                  |   |            | <i>–</i> 67/–78 |            | dB           |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** The inputs are protected by two series connected ESD protection diodes to each power supply. The input current should be limited to less than 1mA. The input voltage should not exceed 200mV beyond the power supply.

**Note 3:** A heat sink may be required to keep the junction temperature below the absolute maximum rating when the output is shorted indefinitely.

**Note 4:** The LTC6268-10I/LTC6269-10I is guaranteed to meet specified performance from -40°C to 85°C. The LTC6268-10H/LTC6269-10H is guaranteed to meet specified performance from -40°C to 125°C.

**Note 5:** Thermal resistance varies with the amount of PC board metal connected to the package. The specified values are for short traces connected to the leads.

**Note 6:** The input bias current is the average of the currents into the positive and negative input pins. Typical measurement is for S8 package.

**Note 7:** Full Power Bandwidth is determined from distortion performance in a gain-of-10 configuration with HD2/HD3 < -40dB (1%) as the criteria for a valid output.

**Note 8:** This parameter is specified by design and/or characterization and is not tested in production.

**Note 9:** The LTC6268-10/LTC6269-10 is capable of producing peak output currents in excess of 135mA. Current density limitations within the IC require the continuous current supplied by the output (sourcing or sinking) over the operating lifetime of the part be limited to under 135mA (Absolute Maximum).

LINEAR TECHNOLOGY

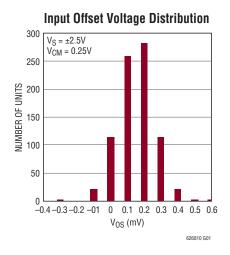

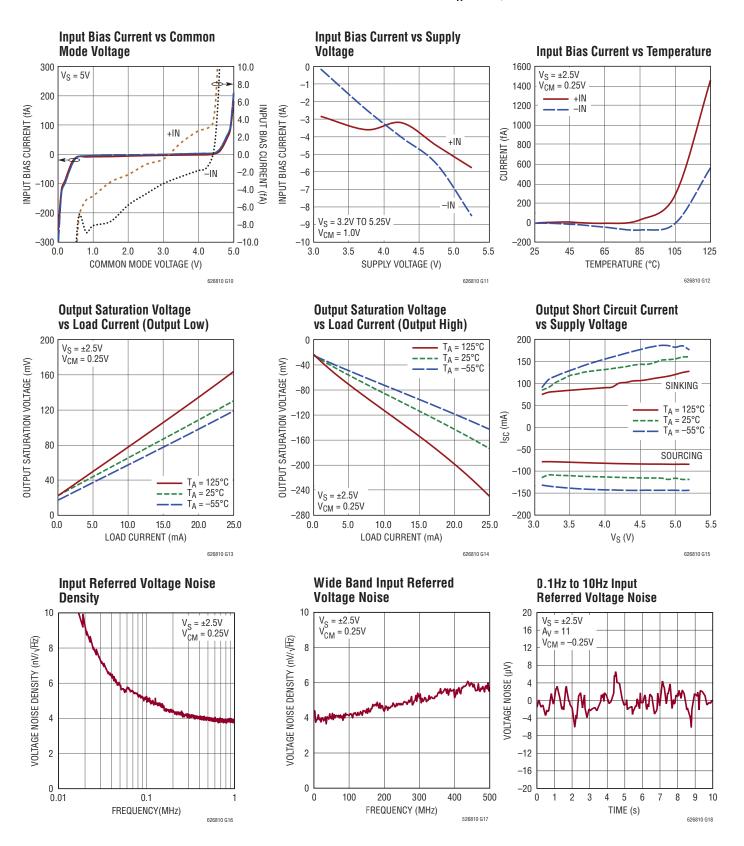

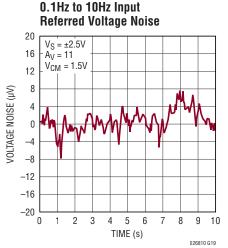

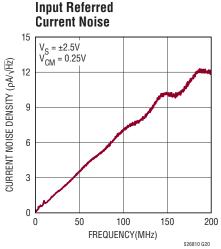

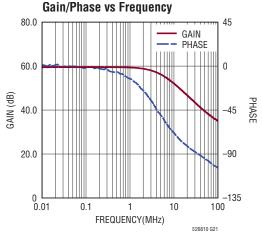

# TYPICAL PERFORMANCE CHARACTERISTICS

$T_A = 25$ °C, unless otherwise noted.

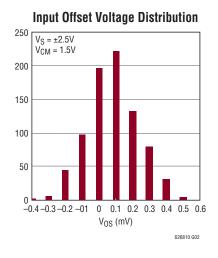

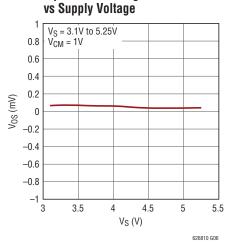

**Input Offset Voltage**

# TYPICAL PERFORMANCE CHARACTERISTICS TA = 25°C, unless otherwise noted.

LINEAR

# TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25$ °C, unless otherwise noted.

#### **Output Impedance** vs Frequency 1000 $A_V = 10V$ $A_{V} = 100V$ 100 OUTPUT IMPEDANCE (Ω) 10 0.1 0.01 0.01 0.001 0.1 10 100 1000 FREQUENCY(MHz)

626810 G22

# TYPICAL PERFORMANCE CHARACTERISTICS T

$T_A = 25$ °C, unless otherwise noted.

#### PIN FUNCTIONS

**–IN:** Inverting Input of the Amplifier. The voltage range of this pin is from  $V^-$  to  $V^+$  –0.5V.

**+IN:** Non-Inverting Input. The voltage range of this pin is from  $V^-$  to  $V^+$  –0.5V.

**V**<sup>+</sup>: Positive Power Supply. Total supply  $(V^+ - V^-)$  voltage is from 3.1V to 5.25V. Split supplies are possible as long as the total voltage between  $V^+$  and  $V^-$  is between 3.1V and 5.25V. A bypass capacitor of  $0.1\mu F$  should be used between  $V^+$  to ground as close to the pin as possible.

**V**<sup>-</sup>: Negative Power Supply. Normally tied to ground, it can also be tied to a voltage other than ground as long

as the voltage difference between V<sup>+</sup> and V<sup>-</sup> is between 3.1V and 5.25V. If it is not connected to ground, bypass it to ground with a capacitor of 0.1 $\mu$ F as close to the pin as possible.

**SHDN**, **SDA**, **SDB**: Active Low op amp shutdown, threshold is 0.75V above the negative supply, V<sup>-</sup>. If left unconnected, the amplifier is enabled.

**OUT:** Amplifier Output.

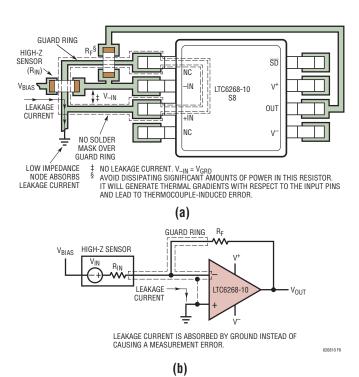

**NC:** Not connected. May be used to create a guard ring around the input to guard against board leakage currents. See Applications Information section for more details.

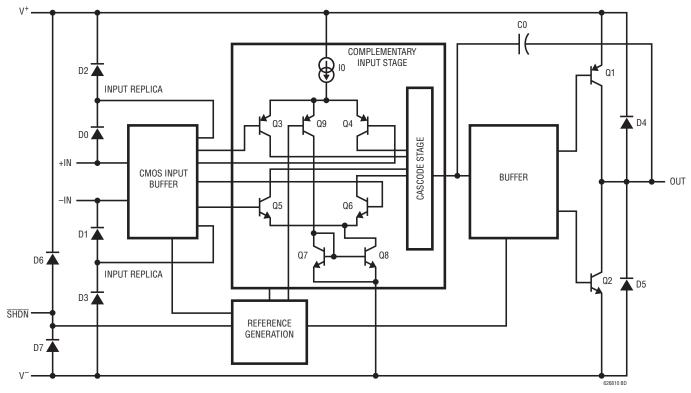

# SIMPLIFIED SCHEMATIC

#### LTC6268-10 Simplified Schematic Diagram

(ONE POLARITY SHOWN IN INPUT PINS)

#### **OPERATION**

The LTC6268-10/LTC6269-10 input signal range is specified from the negative supply to 0.5V below the positive power supply, while the output can swing from rail-to-rail. The schematic above depicts a simplified schematic of the amplifier.

The input pins drive a CMOS buffer stage. The CMOS buffer stage creates replicas of the input voltages to boot strap the protection diodes. In turn, the buffer stage drives a complementary input stage consisting of two differential

amplifiers, active over different ranges of input common mode voltage. The main differential amplifier is active with input common mode voltages from the negative power supply to approximately 1.55V below the positive supply, with the second amplifier active over the remaining range to 0.5V below the positive supply rail. The buffer and output bias stage uses a special compensation technique ensuring stability of the op amp. The common emitter topology of output transistors Q1/Q2 enables the output to swing from rail-to-rail.

#### APPLICATIONS INFORMATION

#### Noise

To minimize the LTC6268-10's noise over a broad range of applications, careful consideration has been placed on input referred voltage noise ( $e_N$ ), input referred current noise ( $i_N$ ) and input capacitance  $C_{IN}$ .

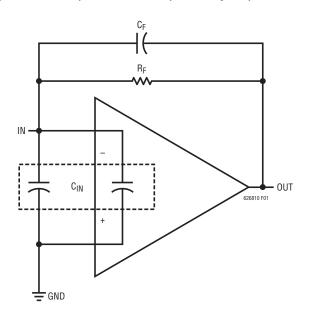

For a transimpedance amplifier (TIA) application such as shown in Figure 1, all three of these op amp parameters, plus the value of feedback resistance  $R_F$ , contribute to noise behavior in different ways, and external components and traces will add to  $C_{IN}$ . It is important to understand the impact of each parameter independently. Input referred

Figure 1. Simplified TIA Schematic

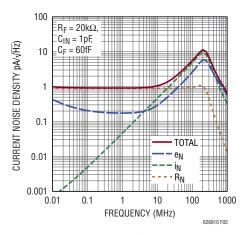

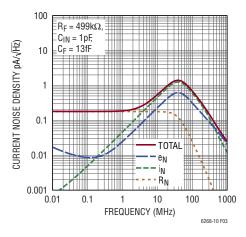

voltage noise (e<sub>N</sub>) consists of flicker noise (or 1/f noise), which dominates at lower frequencies, and thermal noise which dominates at higher frequencies. For LTC6268-10, the 1/f corner, or transition between 1/f and thermal noise. is at 40kHz. The i<sub>N</sub> and R<sub>F</sub> contributions to input referred noise current at the minus input are relatively straight forward, while the e<sub>N</sub> contribution is amplified by the noise gain. Because there is no gain resistor, the noise gain is calculated using feedback resistor(R<sub>F</sub>) in conjunction with impedance of  $C_{IN}$  as  $(1 + 2\pi R_F \cdot C_{IN} \cdot Freq)$ , which increases with frequency. All of the contributions will be limited by the closed loop bandwidth. The equivalent input current noise is shown in Figure 2 and Figure 3, where e<sub>N</sub> represents contribution from input referred voltage noise (e<sub>N</sub>), i<sub>N</sub> represents contribution from input referred current noise (i<sub>N</sub>), and R<sub>F</sub> represents contribution from feedback resistor (R<sub>F</sub>). TIA gain (R<sub>F</sub>) and capacitance at input (C<sub>IN</sub>) are also shown on each figure. Comparing Figure 2 and Figure 3, i<sub>N</sub> dominates at higher frequencies. At lower frequencies, the R<sub>F</sub> contribution dominates. Since average wide band  $e_N$  is  $4.0 \text{nV}/\sqrt{\text{Hz}}$  (see typical performance characteristics), R<sub>F</sub> contribution will become a lesser factor at lower frequencies if  $R_F$  is less than  $860\Omega$  as indicated by the following equation:

$$\frac{eN/R_F}{\sqrt{4kT/R_F}} \ge 1$$

LINEAD

Figure 2

#### Optimizing the Bandwidth for TIA Application

The capacitance at the inverting input node can cause amplifier stability problems if left unchecked. When the feedback around the op amp is resistive ( $R_F$ ), a pole will be created with  $R_F \parallel C_{IN}$ . This pole can create excessive phase shift and possibly oscillation. Referring to Figure 1, the response at the output is:

$$\frac{R_F}{1 + \frac{2\zeta s}{\omega} + \frac{S^2}{\omega^2}}$$

Where  $R_F$  is the DC gain of the TIA,  $\omega$  is the natural frequency of the closed loop, which can be expressed as:

$$\omega = \sqrt{\frac{2\pi GBW}{R_F (C_{IN} + C_F)}}$$

Hence the maximum achievable bandwidth of TIA is:

ftia (Hz) =

$$\sqrt{\frac{\text{GBW}}{2\pi R_{\text{F}}(C_{\text{IN}})}}$$

Figure 3

$\zeta$  is the damping factor of the loop, which can be expressed as:

$$\begin{split} \zeta &= \frac{1}{2} \Bigg( \sqrt{\frac{1}{2\pi GBW \bullet R_F(C_{IN} + C_F)}} \\ &+ R_F \Bigg( C_F + \frac{C_{IN} + C_F}{1 + A_O} \Bigg) \bullet \sqrt{\frac{2\pi GBW}{R_F(C_{IN} + C_F)}} \Bigg) \end{split}$$

Where  $C_{IN}$  is the total capacitance at the inverting input node of the op amp, GBW is the gain bandwidth of the op amp, and  $A_0$  is the DC open loop gain of the op amp.

The small capacitor  $C_F$  in parallel with  $R_F$  can introduce enough damping to stabilize the loop. By assuming  $C_{IN}$  >>  $C_F$ , the following condition needs to be met for  $C_F$ ,

$$C_F > \sqrt{\frac{C_{IN}}{\pi \bullet GBW \bullet R_F}}$$

Since LTC6268-10 is a decompensated op amp with gain-of-10 stable, it requires that  $C_{IN}/C_F \geq 10$ . Table 1 shows the minimum and maximum  $C_F$  for  $R_F$  of 20k and 402k and  $C_{IN}$  of 1pF and 5pF.

Table 1. Min/Max C<sub>F</sub>

| $R_F$ $C_{IN} = 1pF$ |            | $C_{IN} = 5pF$ |

|----------------------|------------|----------------|

| 20kΩ                 | 60fF/100fF | 140fF/500fF    |

| 402kΩ                | 13fF/100fF | 31fF/500fF     |

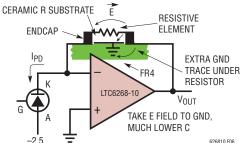

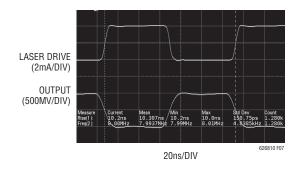

#### Achieving Higher Bandwidth with Higher Gain TIAs

Good layout practices are essential to achieving best results from a TIA circuit. The following two examples show drastically different results from an LTC6268-10 in a 402k TIA. (See Figure 4.) The first example is with an 0805 resistor in a basic circuit layout. In a simple layout, without expending a lot of effort to reduce feedback capacitance, the rise time achieved is about 87ns (Figure 5). implying a bandwidth of 4MHz (BW =  $0.35/t_r$ ). In this case, the bandwidth of the TIA is limited not by the GBW of the LTC6268-10, but rather by the fact that the feedback capacitance is reducing the actual feedback impedance (the TIA gain itself) of the TIA. Basically, it's a resistor bandwidth limitation. The impedance of the  $402k\Omega$  is being reduced by its own parasitic capacitance at high frequency. From the 4MHz bandwidth and the 402k low frequency gain, we can estimate the total feedback capacitance as  $C = 1/(2\pi \cdot 4MHz \cdot 402k\Omega) = 0.1pF$ . That's fairly low, but it can be reduced further.

With some extra layout techniques to reduce feedback capacitance, the bandwidth can be increased. Note that

Figure 4. LTC6268-10 and Low Capacitance Photodiode in a  $402k\Omega$  TIA

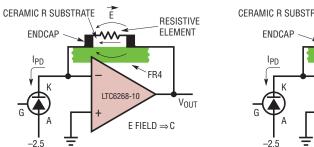

we are increasing the effective "bandwidth" of the 402k resistance. A very powerful method to reduce feedback capacitance is to shield the E field paths that give rise to the capacitance. In this particular case, the method is to place a ground trace between the resistor pads. Such a ground trace shields the output field from getting to the summing node end of the resistor and effectively shunts the field to ground instead. The trace increases the output load capacitance very slightly. See Figure 6 for a pictorial representation.

Figure 7 shows the dramatic increase in bandwidth simply by careful attention to low capacitance methods around the feedback resistance. Bandwidth and rise time went from 4MHz (87ns) to 34MHz (10.3ns), a factor of 8. The ground trace used for LTC6268-10 was much wider than that used in the case of the LTC6268 (see LTC6268 data sheet), extending under the entire resistor dielectric. Assuming all the bandwidth limit is due to feedback capacitance (which isn't fair), we can calculate an upper limit of  $C_f = 1/(2\pi \cdot 402 k\Omega \cdot 34 MHz) = 11.6 fF$ .

Figure 5. Time Domain Response of  $402k\Omega$  TIA without Extra Effort to Reduce Feedback Capacitance. Rise Time Is 87ns and BW Is 4MHz

LINEAR TECHNOLOGY

Figure 6. A Normal Layout at Left and a Field-Shunting Layout at Right. Simply Adding a Ground Trace Under the Feedback Resistor Does Much to Shunt Field Away from the Feedback Side and Dumps It to Ground. Note That the Dielectric Constant of Fr4 and Ceramic Is Typically 4, so Most of the Capacitance Is in the Solids and Not Through the Air. Feedback C is Reduced from 100fF at Left to 11.6fF at Right

#### Maintaining Ultralow Input Bias Current

Leakage currents into high impedance signal nodes can easily degrade measurement accuracy of fA signals. High temperature applications are especially susceptible to these issues. For humid environments, surface coating may be necessary to provide a moisture barrier.

There are several factors to consider in a low input bias current circuit. At the femtoamp level, leakage sources can come from unexpected sources including adjacent signals on the PCB, both on the same layer and from internal layers, any form of contamination on the board from the assembly process or the environment, other components on the signal path and even the plastic of the device package. Care taken in the design of the system can mitigate these sources and achieve excellent performance.

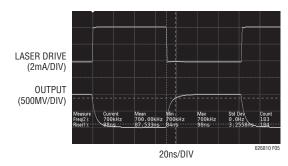

Figure 7. LTC6268-10 in a 402k $\Omega$  TIA with Extra Layout Effort to Reduce Feedback Capacitance Achieves 10.3ns Total System Rise Time, or 34MHz Total System Bandwidth

The choice of device package should be considered because although each has the same die internally, the pin spacing and adjacent signals influence the input bias current. The LTC6268-10/LTC6269-10 is available in SOIC, MSOP. DFN and SOT-23 packages. Of these, the SOIC has been designed as the best choice for low input bias current. It has the largest lead spacing which increases the impedance of the package plastic and the pinout is such that the two input pins are isolated on the far side of the package from the other signals. The gull-wing leads on this package also allow for better cleaning of the PCB and reduced contamination-induced leakage. The other packages have advantages in size and pin count but do so by reducing the input isolation. Leadless packages such as the DFN offer the minimum size but have the smallest pin spacing and may trap contaminants under the package.

The material used in the construction of the PCB can sometimes influence the leakage characteristics of the design. Exotic materials such as Teflon can be used to improve leakage performance in specific cases but they are generally not necessary if some basic rules are applied in the design of conventional FR4 PCBs. It is important to keep the high impedance signal path as short as possible on the board. A node with high impedance is susceptible to picking up any stray signals in the system so keeping it as short as possible reduces this effect. In some cases, it may be necessary to have a metallic shield over this portion of the circuit. However, metallic shielding increases capacitance. Another technique for avoiding leakage paths is to cut slots in the PCB. High impedance circuits are also

susceptible to electrostatic as well as electromagnetic effects. The static charge carried by a person walking by the circuit can induce an interference on the order of 100's of femtoamps. A metallic shield can reduce this effect as well.

The layout of a high impedance input node is very important. Other signals should be routed well away from this signal path and there should be no internal power planes under it. The best defense from coupling signals is distance and this includes vertically as well as on the surface. In cases where the space is limited, slotting the board around the high impedance input nodes can provide additional isolation and reduce the effect of contamination. In electrically noisy environments the use of driven guard rings around these nodes can be effective (see Figure 8). Adding any additional components such as filters to the high impedance input node can increase leakage. The leakage current of a ceramic capacitor is orders of magnitude larger than the bias current of this device. Any filtering will need to be done after this first stage in the signal chain.

#### **Driving Capacitive Load**

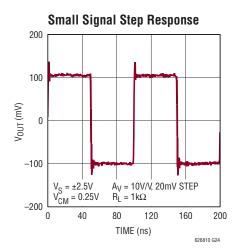

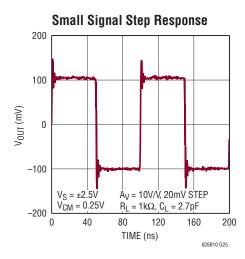

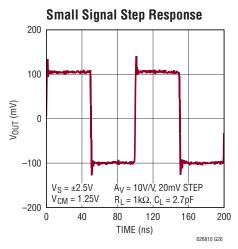

The layout of the output node is also very important since LTC6268-10/LTC6269-10 is very sensitive to capacitive loading due to the very high gain-bandwidth-product. Appreciable ringing will be observed when capacitive loading is more than 5pF.

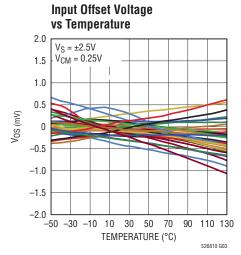

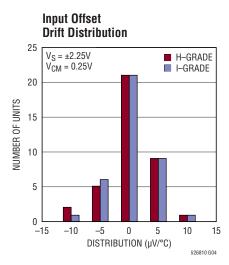

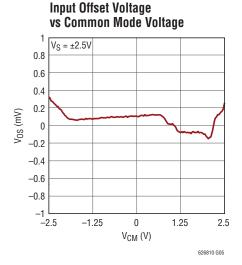

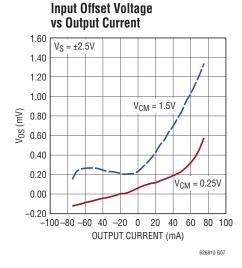

#### **Low Input Offset Voltage**

The LTC6268-10 has a maximum offset voltage of ±2.5mV (PNP region) over temperature. The low offset voltage is essential for precision applications. There are 2 different input stages that are used depending on the input common mode voltage. To increase the versatility of the LTC6268-10, the offset voltages are trimmed for both regions of operation.

Figure 8. Example Layout of Inverting Amplifier (or Transimpedance) with Leakage Guard Ring

#### Rail-to-Rail Output

The LTC6268-10 has a rail-to-rail output stage that has excellent output drive capability. It is capable of delivering over ±40mA of output drive current over temperature. Furthermore, the output can reach within 200mV of either rail while driving ±10mA. Attention must be paid to keep the junction temperature of the IC below 150°C.

#### **Input Protection**

To prevent breakdown of internal devices in the input stage, the two op amp inputs should NOT be separated by more than 2.0V. To help protect the input stage, internal circuitry will engage automatically if the inputs are separated by >2.0V and input currents will begin to flow. In all cases, care should be taken so that these currents remain less than 1mA. Additionally, if only one input is driven, internal circuitry will prevent any breakdown condition under

LINEAD

transient conditions. The worst-case differential input voltage usually occurs when the +input is driven and the output is accidentally shorted to ground while in a unity gain configuration.

#### **ESD**

ESD Protection devices can be seen in the simplified schematic. The +IN and -IN pins use a sophisticated method of ESD protection that incorporates a total of 4 reverse-biased diodes connected as 2 series diodes to each rail. To maintain extremely low input bias currents, the center node of each of these series diode chains is driven by a buffered copy of the input voltage. This maintains the two diodes connected directly to the input pins at low reverse bias, minimizing leakage current of these ESD diodes to the input pins.

The remaining pins have traditional ESD protection, using reverse-biased ESD diodes connected to each power supply rail. Care should be taken to make sure that the voltages on these pins do not exceed the supply voltages by more than 100mV or these diodes will begin to conduct large amounts of current.

#### Shutdown

The LTC6268-10S6, LTC6268-10S8, and LTC6268-10DD have  $\overline{SHDN}$  pins that can shut down the amplifier to less than 1.2mA supply current per amplifier. The  $\overline{SHDN}$  pin voltage needs to be within 0.75V of V<sup>-</sup> for the amplifier to shut down. During shutdown, the output will be in a high output resistance state, so the LTC6268-10 is suitable for multiplexer applications. The internal circuitry is kept in a low current active state for fast recovery. When left floating, the  $\overline{SHDN}$  pin is internally pulled up to the positive supply and the amplifier is enabled.

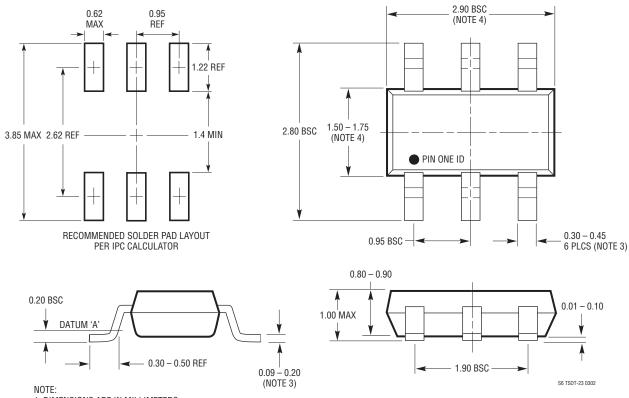

Please refer to http://www.linear.com/designtools/packaging/ for the most recent package drawings.

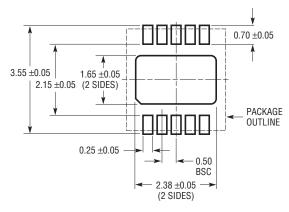

#### S6 Package 6-Lead Plastic TSOT-23

(Reference LTC DWG # 05-08-1636)

- 1. DIMENSIONS ARE IN MILLIMETERS

- 2. DRAWING NOT TO SCALE

- 3. DIMENSIONS ARE INCLUSIVE OF PLATING

- 4. DIMENSIONS ARE EXCLUSIVE OF MOLD FLASH AND METAL BURR

- 5. MOLD FLASH SHALL NOT EXCEED  $0.254 \mathrm{mm}$

- 6. JEDEC PACKAGE REFERENCE IS MO-193

Please refer to http://www.linear.com/designtools/packaging/ for the most recent package drawings.

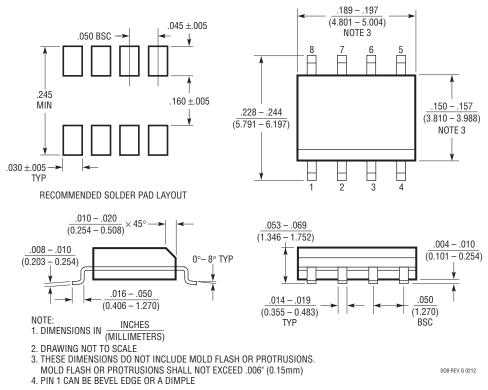

#### S8 Package 8-Lead Plastic Small Outline (Narrow .150 Inch)

(Reference LTC DWG # 05-08-1610 Rev G)

S08 REV G 0212

Please refer to http://www.linear.com/designtools/packaging/ for the most recent package drawings.

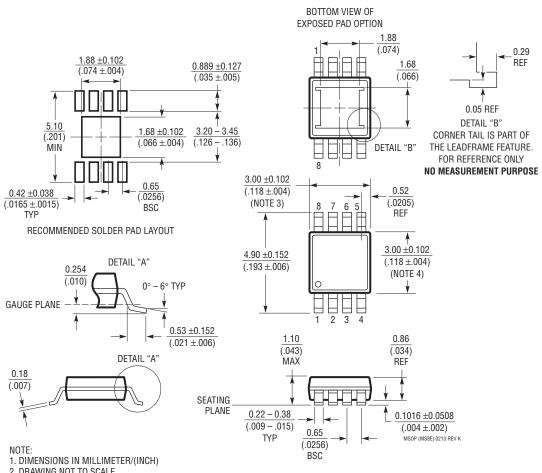

#### **MS8E Package** 8-Lead Plastic MSOP, Exposed Die Pad

(Reference LTC DWG # 05-08-1662 Rev K)

- 2. DRAWING NOT TO SCALE

- 3. DIMENSION DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED 0.152mm (.006") PER SIDE 4. DIMENSION DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS.

- INTERLEAD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.152mm (.006") PER SIDE

- 5. LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.102mm (.004") MAX

- 6. EXPOSED PAD DIMENSION DOES INCLUDE MOLD FLASH. MOLD FLASH ON E-PAD SHALL NOT EXCEED 0.254mm (.010") PER SIDE.

Please refer to http://www.linear.com/designtools/packaging/ for the most recent package drawings.

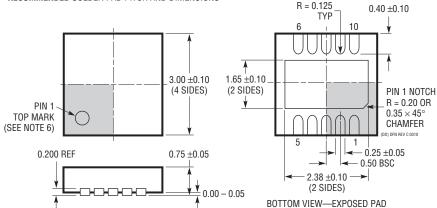

# $\begin{array}{c} \text{DD Package} \\ \text{10-Lead Plastic DFN (3mm} \times \text{3mm)} \end{array}$

(Reference LTC DWG # 05-08-1699 Rev C)

#### NOTE:

- DRAWING TO BE MADE A JEDEC PACKAGE OUTLINE M0-229 VARIATION OF (WEED-2).

CHECK THE LTC WEBSITE DATA SHEET FOR CURRENT STATUS OF VARIATION ASSIGNMENT

- 2. DRAWING NOT TO SCALE

- 3. ALL DIMENSIONS ARE IN MILLIMETERS

- 4. DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE MOLD FLASH. MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE

- 5. EXPOSED PAD SHALL BE SOLDER PLATED

- SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION ON THE TOP AND BOTTOM OF PACKAGE

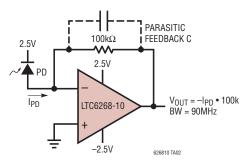

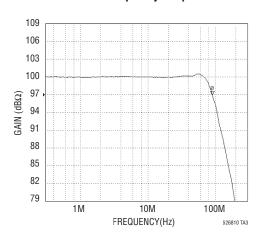

#### TYPICAL APPLICATION

#### 100k $\Omega$ Gain 90MHz Transimpedance Amplifier

PD = OSI OPTOELECTRONICS, FCI-125G-006 OUTPUT NOISE =  $20mV_{P-P}$  MEASURED ON A 100MHz BW

#### $100k\Omega$ TIA Frequency Response

### **RELATED PARTS**

| PART NUMBER                                             | DESCRIPTION                                                           | COMMENTS                                                          |

|---------------------------------------------------------|-----------------------------------------------------------------------|-------------------------------------------------------------------|

| Op Amps                                                 |                                                                       |                                                                   |

| LTC6268/LTC6269                                         | 500MHz Ultra-Low Bias Current FET Input Op Amp                        | Unity Gain Stable, Ultra Low Input Bias Current (3fA), 500MHz GBW |

| LTC6244                                                 | Dual 50MHz, Low Noise, Rail-to-Rail, CMOS Op Amp                      | Unity Gain Stable, 1pA Input Bias Current, 100µV Max Offset.      |

| LTC6240/LTC6241/<br>LTC6242                             | 18MHz, Low Noise, Rail-to-Rail Output, CMOS Op Amp                    | 18MHz GBW, 0.2pA Input Current, 125μV Max Offset.                 |

| LTC6252/LTC6253/<br>LTC6254                             | 720MHz, 3.5mA Power Efficient Rail-to-Rail I/O Op Amp                 | 720MHz GBW, Unity Gain Stable, Low Noise                          |

| LTC6246/LTC6247/<br>LTC6248                             | 180MHz, 1mA Power Efficient Rail-to-Rail I/O Op Amps                  | 180MHz GBW, Unity Gain Stable, Low Noise                          |

| LT1818                                                  | 400MHz, 2500V/μs, 9mA Single Operational Amplifier                    | Unity Gain Stable, 6nV/√Hz Unity Gain Stable                      |

| LT6236                                                  | 215MHz, Rail-to-Rail Output, 1.1nV/\(\sqrt{Hz}\), 3.5mA Op Amp Family | 350μV Max Offset Voltage, 3V to 12.6V Supply                      |

| LT6411                                                  | 650MHz Differential ADC Driver/Dual Selectable Amplifier              | SR 3300V/µs, 6ns 0.1% Settling.                                   |

| SAR ADC                                                 |                                                                       |                                                                   |

| LTC2376-18/<br>LTC2377-18/<br>LTC2378-18/<br>LTC2379-18 | 18-Bit, 250ksps to 1.6Msps, Low Power SAR ADC, 102dB SNR              | 18mW at 1.6Msps, 3.4μW at 250sps, -126dB THD.                     |