# LC<sup>2</sup>MOS Precision Quad SPST Switches

## **ADG413**

#### **FEATURES**

44 V supply maximum ratings ±15 V analog signal range Low on resistance (< 35 Ω) Ultralow power dissipation (35 μW) Fast switching times tor < 175 ns tor < 145 ns TTL-/CMOS-compatible Plug-in replacement for DG411/DG412/DG413

#### **APPLICATIONS**

Audio and video switching Automatic test equipment Precision data acquisition Battery-powered systems Sample-and-hold systems Communication systems

#### **GENERAL DESCRIPTION**

The ADG411, ADG412, and ADG413 are monolithic CMOS devices comprising four independently selectable switches. They are designed on an enhanced LC<sup>2</sup>MOS process which provides low power dissipation yet gives high switching speed and low on resistance.

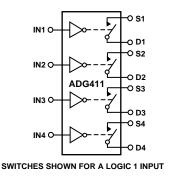

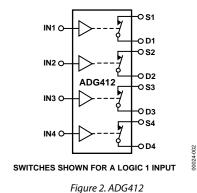

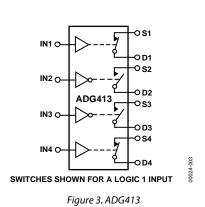

The on resistance profile is very flat over the full analog input range ensuring excellent linearity and low distortion when switching audio signals. Fast switching speed coupled with high signal bandwidth also make the parts suitable for video signal switching. CMOS construction ensures ultralow power dissipation, making the parts ideally suited for portable and battery-powered instruments. The ADG411, ADG412, and ADG413 contain four independent SPST switches. The ADG411 and ADG412 differ only in that the digital control logic is inverted. The ADG411 switches are turned on with a logic low on the appropriate control input, while a logic high is required for the ADG412. The ADG413 has two switches with digital control logic similar to that of the ADG411 while the logic is inverted on the other two switches.

Each switch conducts equally well in both directions when on, and each has an input signal range that extends to the supplies. In the off condition, signal levels up to the supplies are blocked. All switches exhibit break-before-make switching action for use in multiplexer applications. Inherent in the design is low charge injection for minimum transients when switching the digital inputs.

#### **PRODUCT HIGHLIGHTS**

1. Extended signal range

The ADG411, ADG412, and ADG413 are fabricated on an enhanced LC<sup>2</sup>MOS, giving an increased signal range which extends fully to the supply rails.

- 2. Ultralow power dissipation

- $3. \ Low \ R_{\rm ON}$

- Break-before-make switching This prevents channel shorting when the switches are configured as a multiplexer.

- 5. Single-supply operation

For applications where the analog signal is unipolar, the ADG411, ADG412, and ADG413 can be operated from a single-rail power supply. The parts are fully specified with a single 12 V power supply and remain functional with single supplies as low as 5 V.

Figure 1. ADG411

#### FUNCTIONAL BLOCK DIAGRAMS

Rev. D

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113

©2010 Analog Devices, Inc. All rights reserved.

### TABLE OF CONTENTS

| Features                  | . 1 |

|---------------------------|-----|

| Applications              | . 1 |

| General Description       | . 1 |

| Product Highlights        | . 1 |

| Functional Block Diagrams | . 1 |

| Revision History          | . 2 |

| Specifications            | . 3 |

| Dual Supply               | . 3 |

| Single Supply             | . 4 |

|                           |     |

### **REVISION HISTORY**

| 6/10—Rev. C to Rev. D                 |           |

|---------------------------------------|-----------|

| Updated Outline Dimensions            |           |

| Changes to Ordering Guide             |           |

| 11/04—Rev. B to Rev. C                |           |

| Format Updated                        | Universal |

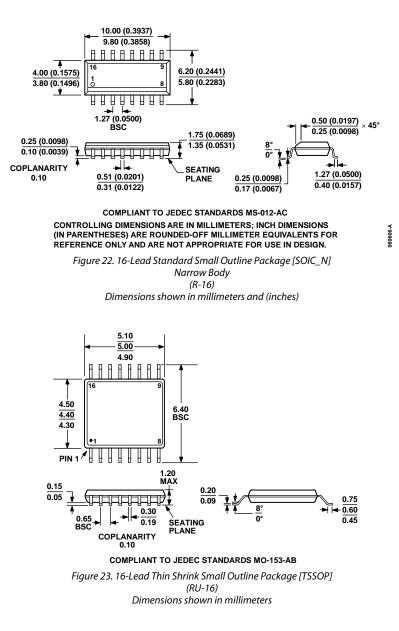

| Change to Package Drawing (Figure 23) |           |

| Changes to Ordering Guide             |           |

| 7/04—Rev. A to Rev. B                 |           |

| Changes to ORDERING GUIDE             | 5         |

| Updated OUTLINE DIMENSIONS            |           |

| Absolute Maximum Ratings                    | 5  |

|---------------------------------------------|----|

| ESD Caution                                 | 5  |

| Pin Configuration and Function Descriptions | 6  |

| Typical Performance Characteristics         | 7  |

| Terminology                                 | 9  |

| Applications                                | 10 |

| Test Circuits                               | 11 |

| Outline Dimensions                          | 13 |

| Ordering Guide                              | 15 |

### **SPECIFICATIONS**

### **DUAL SUPPLY**

$V_{\text{DD}}$  = 15 V  $\pm$  10%,  $V_{\text{SS}}$  = –15 V  $\pm$  10%,  $V_{\text{L}}$  = 5 V  $\pm$  10%, GND = 0 V, unless otherwise noted.  $^{1}$

#### Table 1.

|                                                               | B Version |                                    | T Version |                                    |        |                                                                                                                         |

|---------------------------------------------------------------|-----------|------------------------------------|-----------|------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------|

| Parameter                                                     | +25°C     | –40°C to<br>+85°C                  | +25℃      | –55°C to<br>+125°C                 | Unit   | Test Conditions/Comments                                                                                                |

| ANALOG SWITCH                                                 | 725 C     | +0J C                              | +2J C     | +125 C                             |        | Test conditions/comments                                                                                                |

| Analog Signal Range                                           |           | V <sub>DD</sub> to V <sub>SS</sub> |           | V <sub>DD</sub> to V <sub>SS</sub> | v      |                                                                                                                         |

| Ron                                                           | 25        |                                    | 25        |                                    | Ωtyp   | $V_D = \pm 8.5 V$ , $I_S = -10 mA$ ;                                                                                    |

|                                                               | 35        | 45                                 | 35        | 45                                 | Ωmax   | $V_{DD} = +13.5 \text{ V}, \text{ V}_{SS} = -13.5 \text{ V}$                                                            |

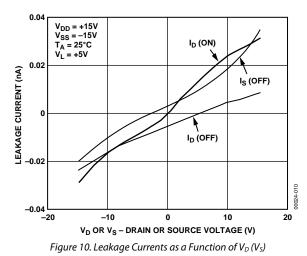

| LEAKAGE CURRENTS                                              |           |                                    |           |                                    |        | $V_{DD} = +16.5 \text{ V}, \text{V}_{SS} = -16.5 \text{ V}$                                                             |

| Source OFF Leakage I₅ (OFF)                                   | ±0.1      |                                    | ±0.1      |                                    | nA typ | $V_D = +15.5 V/-15.5 V,$<br>$V_S = -15.5 V/+15.5 V;$                                                                    |

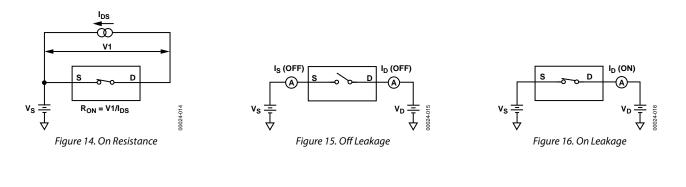

|                                                               | ±0.25     | ±0.25                              | ±0.25     | ±20                                | nA max | Figure 15                                                                                                               |

| Drain OFF Leakage I <sub>D</sub> (OFF)                        | ±0.1      |                                    | ±0.1      |                                    | nA typ | $    V_D = +15.5 \text{ V}/-15.5 \text{ V}, \\     V_S = -15.5 \text{ V}/+15.5 \text{ V}; $                             |

|                                                               | ±0.25     | ±5                                 | ±0.25     | ±20                                | nA max | Figure 15                                                                                                               |

| Channel ON Leakage ID, Is (ON)                                | ±0.1      |                                    | ±0.1      |                                    | nA typ | $V_D = V_S = +15.5 \text{ V/}-15.5 \text{ V};$                                                                          |

|                                                               | ±0.4      | ±10                                | ±0.4      | ± 40                               | nA max | Figure 16                                                                                                               |

| DIGITAL INPUTS                                                |           |                                    |           |                                    |        |                                                                                                                         |

| Input High Voltage, V <sub>INH</sub>                          |           | 2.4                                |           | 2.4                                | V min  |                                                                                                                         |

| Input Low Voltage, $V_{INL}$                                  |           | 0.8                                |           | 0.8                                | V max  |                                                                                                                         |

| Input Current                                                 |           |                                    |           |                                    |        |                                                                                                                         |

| I <sub>INL</sub> or I <sub>INH</sub>                          | 0.005     |                                    | 0.005     |                                    | μA typ | $V_{IN} = V_{INL} \text{ or } V_{INH}$                                                                                  |

|                                                               |           | ±0.5                               |           | ±0.5                               | μA max |                                                                                                                         |

| DYNAMIC CHARACTERISTICS <sup>2</sup>                          |           |                                    |           |                                    |        |                                                                                                                         |

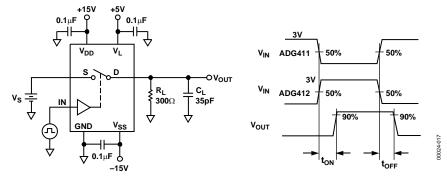

| ton                                                           | 110       |                                    | 110       |                                    | ns typ | $R_L = 300 \Omega$ , $C_L = 35 pF$ ;                                                                                    |

|                                                               |           | 175                                |           | 175                                | ns max | $V_s = \pm 10 V$ ; Figure 17                                                                                            |

| toff                                                          | 100       |                                    | 100       |                                    | ns typ | $R_L = 300 \Omega$ , $C_L = 35 pF$ ;                                                                                    |

|                                                               |           | 145                                |           | 145                                | ns max | $V_s = \pm 10 V$ ; Figure 17                                                                                            |

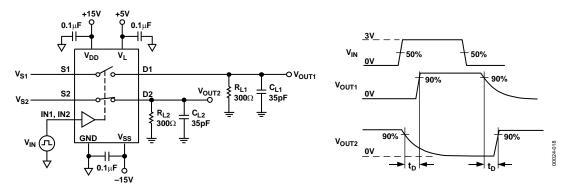

| Break-Before-Make Time Delay, t <sub>D</sub><br>(ADG413 Only) | 25        |                                    | 25        |                                    | ns typ | $\begin{array}{l} R_L = 300 \; \Omega,  C_L = 35 \; pF; \\ V_{S1} = V_{S2} = 10 \; V;  Figure \; 18 \end{array}$        |

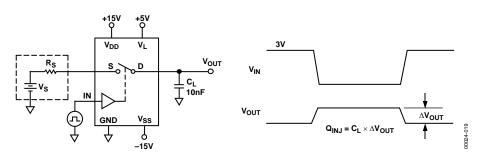

| Charge Injection                                              | 5         |                                    | 5         |                                    | pC typ | $V_{s} = 0 V, R_{s} = 0 \Omega, C_{L} = 10 nF;$<br>Figure 19                                                            |

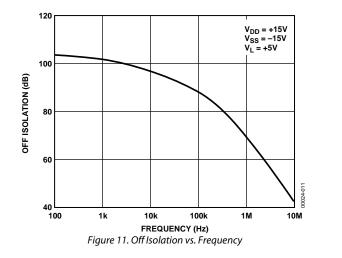

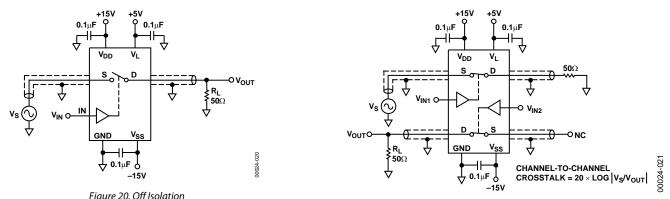

| OFF Isolation                                                 | 68        |                                    | 68        |                                    | dB typ | $\label{eq:RL} \begin{array}{l} R_{L} = 50 \; \Omega,  C_{L} = 5 \; pF,  f = 1 \; MHz; \\ \text{Figure 20} \end{array}$ |

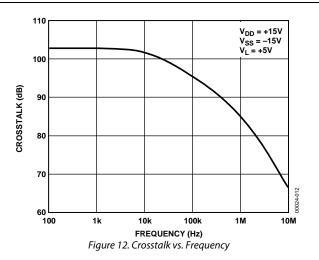

| Channel-to-Channel Crosstalk                                  | 85        |                                    | 85        |                                    | dB typ | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 1 MHz$ ;<br>Figure 21                                                           |

| C <sub>s</sub> (OFF)                                          | 9         |                                    | 9         |                                    | pF typ | f = 1 MHz                                                                                                               |

| C <sub>D</sub> (OFF)                                          | 9         |                                    | 9         |                                    | pF typ | f = 1 MHz                                                                                                               |

| C <sub>D</sub> , C <sub>S</sub> (ON)                          | 35        |                                    | 35        |                                    | pF typ | f = 1 MHz                                                                                                               |

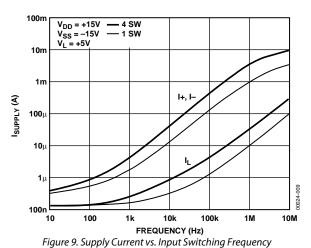

| POWER REQUIREMENTS                                            |           |                                    |           |                                    |        | $V_{\text{DD}} = +16.5 \text{ V}, V_{\text{SS}} = -16.5 \text{ V}; \text{ Digital}$ inputs = 0 V or 5 V                 |

| lod                                                           | 0.0001    |                                    | 0.0001    |                                    | μA typ |                                                                                                                         |

|                                                               | 1         | 5                                  | 1         | 5                                  | µA max |                                                                                                                         |

| lss                                                           | 0.0001    |                                    | 0.0001    |                                    | μA typ |                                                                                                                         |

|                                                               | 1         | 5                                  | 1         | 5                                  | μA max |                                                                                                                         |

| ۱L                                                            | 0.0001    |                                    | 0.0001    |                                    | μA typ |                                                                                                                         |

|                                                               | 1         | 5                                  | 1         | 5                                  | μA max |                                                                                                                         |

$^1$  Temperature ranges are as follows: B versions: –40°C to +85°C; T versions: –55°C to +125°C.  $^2$  Guaranteed by design; not subject to production test.

#### SINGLE SUPPLY

$V_{\text{DD}}$  = 12 V  $\pm$  10%,  $V_{\text{SS}}$  = 0 V,  $V_{\text{L}}$  = 5 V  $\pm$  10%, GND = 0 V, unless otherwise noted.  $^{1}$

#### Table 2.

|                                                         | <b>B</b> Version |                        | T Version |                        |        |                                                                               |

|---------------------------------------------------------|------------------|------------------------|-----------|------------------------|--------|-------------------------------------------------------------------------------|

| Parameter                                               | +25°C            | –40°C to + 85°C        | +25°C     | –55°C to +125°C        | Unit   | Test Conditions/Comments                                                      |

| ANALOG SIGNAL RANGE                                     |                  | 0 V to V <sub>DD</sub> |           | 0 V to V <sub>DD</sub> | V      |                                                                               |

| R <sub>ON</sub>                                         | 40               |                        | 40        |                        | Ωtyp   | $0 < V_D = 8.5 V$ , $I_S = -10 mA$ ;                                          |

|                                                         | 80               | 100                    | 80        | 100                    | Ωmax   | $V_{DD} = 10.8 V$                                                             |

| LEAKAGE CURRENTS                                        |                  |                        |           |                        |        | V <sub>DD</sub> = 13.2 V                                                      |

| Source OFF Leakage Is (OFF)                             | ±0.1             |                        | ±0.1      |                        | nA typ | $V_D = 12.2 V/1 V, V_S = 1 V/12.2 V_s$                                        |

|                                                         | ±0.25            | ±5                     | ±0.25     | ±20                    | nA max | Figure 15                                                                     |

| Drain OFF Leakage I <sub>D</sub> (OFF)                  | ±0.1             |                        | ±0.1      |                        | nA typ | $V_D = 12.2 V/1 V, V_S = 1 V/12.2 V$                                          |

|                                                         | ±0.25            | ±5                     | ±0.25     | ±20                    | nA max | Figure 15                                                                     |

| Channel ON Leakage I <sub>D</sub> , I <sub>S</sub> (ON) | ±0.1             |                        | ±0.1      |                        | nA typ | $V_D = V_S = 12.2 \text{ V/1 V};$                                             |

|                                                         | ±0.4             | ±10                    | ±0.4      | ±40                    | nA max | Figure 16                                                                     |

| DIGITAL INPUTS                                          |                  |                        |           |                        |        |                                                                               |

| Input High Voltage, V <sub>INH</sub>                    |                  | 2.4                    |           | 2.4                    | V min  |                                                                               |

| Input Low Voltage, VINL                                 |                  | 0.8                    |           | 0.8                    | V max  |                                                                               |

| Input Current                                           |                  |                        |           |                        |        |                                                                               |

| Inl or Inh                                              | 0.005            |                        | 0.005     |                        | μA typ | $V_{IN} = V_{INL} \text{ or } V_{INH}$                                        |

|                                                         |                  | ±0.5                   |           | ±0.5                   | µA max |                                                                               |

| DYNAMIC CHARACTERISTICS <sup>2</sup>                    |                  |                        |           |                        |        |                                                                               |

| ton                                                     | 175              |                        | 175       |                        | ns typ | $R_L = 300 \Omega, C_L = 35 pF;$                                              |

|                                                         |                  | 250                    |           | 250                    | ns max | V <sub>s</sub> = 8 V; Figure 17                                               |

| toff                                                    | 95               |                        | 95        |                        | ns typ | $R_{L} = 300 \Omega, C_{L} = 35 pF;$                                          |

|                                                         |                  | 125                    |           | 125                    | ns max | V <sub>s</sub> = 8 V; Figure 17                                               |

| Break-Before-Make Time<br>Delay, t⊳ (ADG413 Only)       | 25               |                        | 25        |                        | ns typ | $R_L = 300 \Omega$ , $C_L = 35 pF$ ;<br>$V_{s1} = V_{s2} = +10 V$ ; Figure 18 |

| Charge Injection                                        | 25               |                        | 25        |                        | pC typ | $V_s = 0 V$ , $R_s = 0 \Omega$ , $C_L = 10 nF$ ;<br>Figure 19                 |

| OFF Isolation                                           | 68               |                        | 68        |                        | dB typ | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 1 MHz$ ;<br>Figure 20                 |

| Channel-to-Channel Crosstalk                            | 85               |                        | 85        |                        | dB typ | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 1 MHz$ ;<br>Figure 21                 |

| C <sub>s</sub> (OFF)                                    | 9                |                        | 9         |                        | pF typ | f = 1 MHz                                                                     |

| C <sub>D</sub> (OFF)                                    | 9                |                        | 9         |                        | pF typ | f = 1 MHz                                                                     |

| C <sub>D</sub> , C <sub>S</sub> (ON)                    | 35               |                        | 35        |                        | pF typ | f = 1 MHz                                                                     |

| POWER REQUIREMENTS                                      |                  |                        |           |                        |        | V <sub>DD</sub> = 13.2 V;<br>Digital inputs = 0 V or 5 V                      |

| IDD                                                     | 0.0001           |                        | 0.0001    |                        | μA typ |                                                                               |

|                                                         | 1                | 5                      | 1         | 5                      | μA max |                                                                               |

| lı.                                                     | 0.0001           |                        | 0.0001    |                        | μA typ |                                                                               |

|                                                         | 1                | 5                      | 1         | 5                      | µA max | $V_L = 5.25 V$                                                                |

<sup>1</sup> Temperature ranges are as follows: B versions:-40°C to +85°C; T versions: -55°C to +125°C. <sup>2</sup> Guaranteed by design; not subject to production test.

#### Table 4. Truth Table (ADG413) Table 3. Truth Table (ADG411/ADG412) Switch 1, 4 Logic Switch 2, 3 ADG411 In ADG412 In **Switch Condition** 0 OFF ON ON 0 1 1 ON OFF 1 0 OFF

### ABSOLUTE MAXIMUM RATINGS

$T_A = 25^{\circ}C$ , unless otherwise noted.

#### Table 5.

| Parameters                                                | Ratings                                                                               |

|-----------------------------------------------------------|---------------------------------------------------------------------------------------|

| V <sub>DD</sub> to V <sub>SS</sub>                        | 44 V                                                                                  |

| V <sub>DD</sub> to GND                                    | –0.3 V to +25 V                                                                       |

| Vss to GND                                                | +0.3 V to -25 V                                                                       |

| $V_L$ to GND                                              | -0.3 V to V <sub>DD</sub> + 0.3 V                                                     |

| Analog, Digital Inputs <sup>1</sup>                       | V <sub>ss</sub> – 2 V to V <sub>DD</sub> + 2 V or<br>30 mA, whichever<br>occurs first |

| Continuous Current, S or D                                | 30 mA                                                                                 |

| Peak Current, S or D (Pulsed at 1 ms, 10% Duty Cycle max) | 100 mA                                                                                |

| Operating Temperature Range                               |                                                                                       |

| Industrial (B Version)                                    | -40°C to +85°C                                                                        |

| Extended (T Version)                                      | –55°C to +125°C                                                                       |

| Storage Temperature Range                                 | –65°C to +150°C                                                                       |

| Junction Temperature                                      | 150°C                                                                                 |

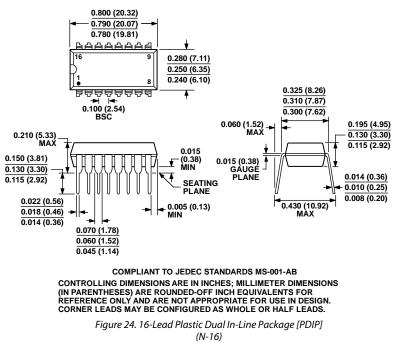

| PDIP, Power Dissipation                                   | 470 mW                                                                                |

| $\theta_{JA}$ Thermal Impedance                           | 117°C/W                                                                               |

| Lead Temperature, Soldering (10 s)                        | 260°C                                                                                 |

| SOIC Package, Power Dissipation                           | 600 mW                                                                                |

| $\theta_{JA}$ Thermal Impedance                           | 77°C/W                                                                                |

| TSSOP Package, Power Dissipation                          | 450 mW                                                                                |

| θ <sub>JA</sub> Thermal Impedance                         | 115°C/W                                                                               |

| $\theta_{JC}$ Thermal Impedance                           | 35°C/W                                                                                |

| Lead Temperature, Soldering                               |                                                                                       |

| Vapor Phase (60 s)                                        | 215°C                                                                                 |

| Infrared (15 s)                                           | 220°C                                                                                 |

<sup>1</sup> Overvoltages at IN, S, or D are clamped by internal diodes. Current should be limited to the maximum ratings given.

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Only one absolute maximum rating may be applied at any one time.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

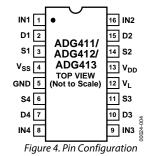

### **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

#### Table 6. Pin Function Descriptions

| Pin No.      | Mnemonic        | Description                                                                                                       |

|--------------|-----------------|-------------------------------------------------------------------------------------------------------------------|

| 1, 8, 9, 16  | IN1–IN4         | Logic Control Input.                                                                                              |

| 2, 7, 10, 15 | D1-D4           | Drain Terminal. Can be an input or output.                                                                        |

| 3, 6, 11, 14 | S1–S4           | Source Terminal. Can be an input or output.                                                                       |

| 4            | V <sub>SS</sub> | Most Negative Power Supply Potential in Dual Supplies. In single supply applications, it may be connected to GND. |

| 5            | GND             | Ground (0 V) Reference.                                                                                           |

| 12           | VL              | Logic Power Supply (5 V).                                                                                         |

| 13           | V <sub>DD</sub> | Most Positive Power Supply Potential.                                                                             |

### **TYPICAL PERFORMANCE CHARACTERISTICS**

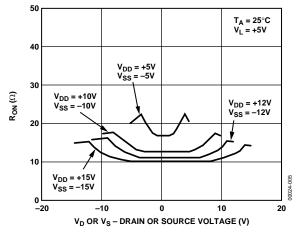

Figure 5. On Resistance as a Function of V<sub>D</sub> (V<sub>s</sub>) Dual Supplies

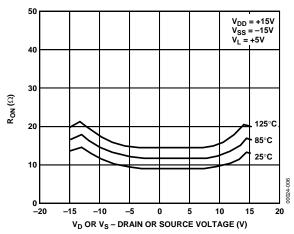

Figure 6. On Resistance as a Function of  $V_D$  ( $V_S$ ) for Different Temperatures

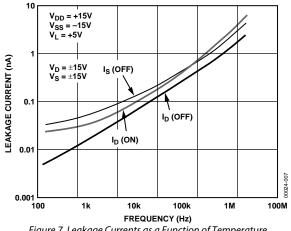

Figure 7. Leakage Currents as a Function of Temperature

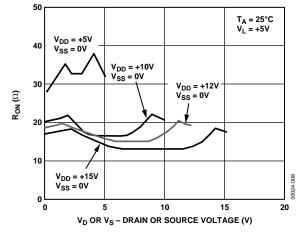

Figure 8. On Resistance as a Function of V<sub>D</sub> (V<sub>s</sub>) Single Supply

### TERMINOLOGY

Ron Ohmic resistance between D and S. Is (OFF) Source leakage current with the switch OFF. I<sub>D</sub> (OFF) Drain leakage current with the switch OFF. ID, Is (ON) Channel leakage current with the switch ON.  $V_D(V_s)$ Analog voltage on terminals D, S. Cs (OFF) OFF switch source capacitance. C<sub>D</sub> (OFF) OFF switch drain capacitance.  $C_D, C_S(ON)$ ON switch capacitance.

#### ton

Delay between applying the digital control input and the output switching on.

#### toff

Delay between applying the digital control input and the output switching off.

#### t<sub>D</sub>

OFF time or ON time measured between the 90% points of both switches, when switching from one address state to another.

#### Crosstalk

A measure of unwanted signal which is coupled through from one channel to another as a result of parasitic capacitance.

#### **Off Isolation**

A measure of unwanted signal coupling through an OFF switch.

#### **Charge Injection**

A measure of the glitch impulse transferred from the digital input to the analog output during switching.

### **APPLICATIONS**

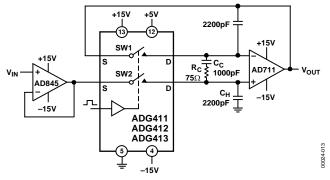

Figure 13 illustrates a precise, fast, sample-and-hold circuit. An AD845 is used as the input buffer while the output operational amplifier is an AD711. During the track mode, SW1 is closed and the output  $V_{\rm OUT}$  follows the input signal  $V_{\rm IN}$ . In the hold mode, SW1 is opened and the signal is held by the hold capacitor  $C_{\rm H}$ .

Due to switch and capacitor leakage, the voltage on the hold capacitor decreases with time. The ADG411/ADG412/ADG413 minimizes this droop due to its low leakage specifications. The droop rate is further minimized by the use of a polystyrene hold capacitor. The droop rate for the circuit shown is typically  $30 \mu V/\mu s$ .

A second switch, SW2, which operates in parallel with SW1, is included in this circuit to reduce pedestal error. Since both switches are at the same potential, they have a differential effect on the op amp AD711, which minimizes charge injection effects. Pedestal error is also reduced by the compensation network  $R_c$  and  $C_c$ . This compensation network also reduces the hold time glitch while optimizing the acquisition time. Using the illustrated op amps and component values, the pedestal error has a maximum value of 5 mV over the  $\pm 10$  V input range. Both the acquisition and settling times are 850 ns.

Figure 13. Fast, Accurate Sample-and-Hold

### **TEST CIRCUITS**

Figure 17. Switching Times

Figure 18. Break-Before-Make Time Delay

Figure 19. Charge Injection

Figure 20. Off Isolation

Figure 21. Channel-to-Channel Crosstalk

### **OUTLINE DIMENSIONS**

Dimensions shown in inches and (millimeters)

073106-B

#### **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description | Package Option |

|--------------------|-------------------|---------------------|----------------|

| ADG411BN           | -40°C to +85°C    | 16-Lead P-DIP       | N-16           |

| ADG411BNZ          | -40°C to +85°C    | 16-Lead P-DIP       | N-16           |

| ADG411BR           | -40°C to +85°C    | 16-Lead SOIC_N      | R-16           |

| ADG411BR-REEL      | -40°C to +85°C    | 16-Lead SOIC_N      | R-16           |

| ADG411BR-REEL7     | -40°C to +85°C    | 16-Lead SOIC_N      | R-16           |

| ADG411BRZ          | -40°C to +85°C    | 16-Lead SOIC_N      | R-16           |

| ADG411BRZ-REEL     | -40°C to +85°C    | 16-Lead SOIC_N      | R-16           |

| ADG411BRZ-REEL7    | -40°C to +85°C    | 16-Lead SOIC_N      | R-16           |

| ADG411BRU          | -40°C to +85°C    | 16-Lead TSSOP       | RU-16          |

| ADG411BRU-REEL     | -40°C to +85°C    | 16-Lead TSSOP       | RU-16          |

| ADG411BRU-REEL7    | -40°C to +85°C    | 16-Lead TSSOP       | RU-16          |

| ADG411BRUZ         | -40°C to +85°C    | 16-Lead TSSOP       | RU-16          |

| ADG411BRUZ-REEL    | -40°C to +85°C    | 16-Lead TSSOP       | RU-16          |

| ADG411BRUZ-REEL7   | -40°C to +85°C    | 16-Lead TSSOP       | RU-16          |

| ADG411BCHIPS       |                   | DIE                 |                |

| ADG412BN           | -40°C to +85°C    | 16-Lead P-DIP       | N-16           |

| ADG412BNZ          | -40°C to +85°C    | 16-Lead P-DIP       | N-16           |

| ADG412BR           | -40°C to +85°C    | 16-Lead SOIC_N      | R-16           |

| ADG412BR-REEL      | -40°C to +85°C    | 16-Lead SOIC_N      | R-16           |

| ADG412BR-REEL7     | -40°C to +85°C    | 16-Lead SOIC_N      | R-16           |

| ADG412BRZ          | -40°C to +85°C    | 16-Lead SOIC_N      | R-16           |

| ADG412BRZ-REEL     | -40°C to +85°C    | 16-Lead SOIC_N      | R-16           |

| ADG412BRZ-REEL7    | -40°C to +85°C    | 16-Lead SOIC_N      | R-16           |

| ADG412BRU          | -40°C to +85°C    | 16-Lead TSSOP       | RU-16          |

| ADG412BRU-REEL     | -40°C to +85°C    | 16-Lead TSSOP       | RU-16          |

| ADG412BRU-REEL7    | -40°C to +85°C    | 16-Lead TSSOP       | RU-16          |

| ADG412BRUZ         | -40°C to +85°C    | 16-Lead TSSOP       | RU-16          |

| ADG412BRUZ-REEL    | -40°C to +85°C    | 16-Lead TSSOP       | RU-16          |

| ADG412BRUZ-REEL7   | -40°C to +85°C    | 16-Lead TSSOP       | RU-16          |

| ADG413BN           | -40°C to +85°C    | 16-Lead P-DIP       | N-16           |

| ADG413BNZ          | -40°C to +85°C    | 16-Lead P-DIP       | N-16           |

| ADG413BR           | -40°C to +85°C    | 16-Lead SOIC_N      | R-16           |

| ADG413BR-REEL      | -40°C to +85°C    | 16-Lead SOIC_N      | R-16           |

| ADG413BRZ          | -40°C to +85°C    | 16-Lead SOIC_N      | R-16           |

| ADG413BRZ-REEL     | -40°C to +85°C    | 16-Lead SOIC_N      | R-16           |

| ADG413BRUZ         | -40°C to +85°C    | 16-Lead TSSOP       | RU-16          |

| ADG413BRUZ-500RL7  | -40°C to +85°C    | 16-Lead TSSOP       | RU-16          |

| ADG413BRUZ-REEL    | -40°C to +85°C    | 16-Lead TSSOP       | RU-16          |

| ADG413BRUZ-REEL7   | -40°C to +85°C    | 16-Lead TSSOP       | RU-16          |

$^{1}$ Z = RoHS Compliant Part.

### NOTES

©2010 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D00024-0-6/10(D)

www.analog.com

Rev. D | Page 16 of 16